MITOUJTAGとは何か

製品について

ご購入を検討中の方へ

サポート

JTAGについて

JTAG技術サービス(有料)

JTAG開発日記

JTAGを熱く語る

LVDSのバウンダリスキャン

最近のFPGAはLVDSをサポートしています。LVDSに設定した端子をバウンダリスキャンしたらどうなるのでしょうか?

ここではXILINXの最新FPGAであるZYNQを用いて検証しました。

出力に設定した場合

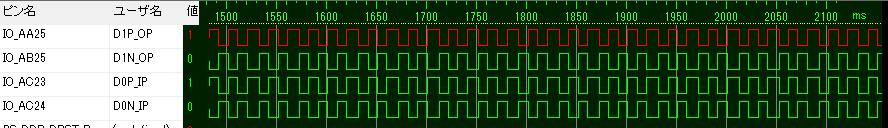

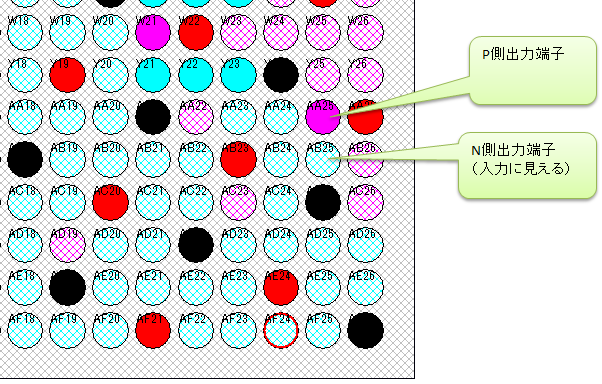

LVDSの出力に設定された端子は、バウンダリスキャンではP側のみ操作でき、N側は入力であるように見えてしまいます。

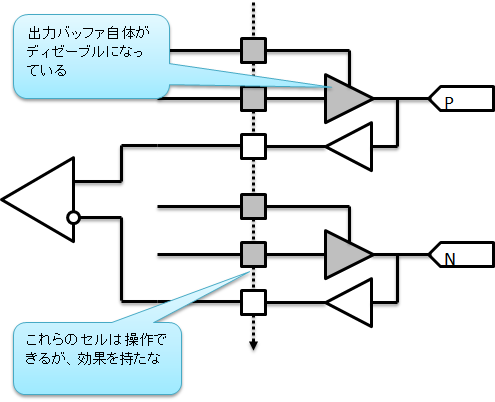

図1 LVDSのN側端子は入力として見えてしまう

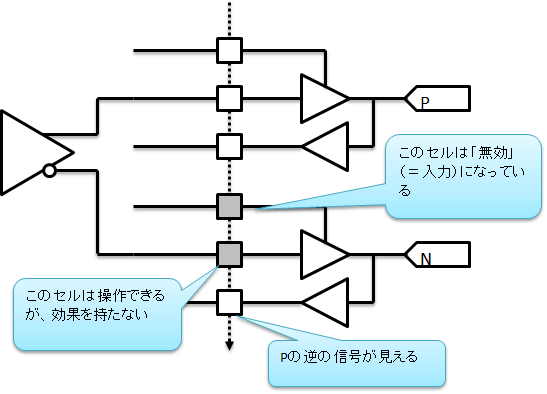

なぜならば、N側端子のバウンダリスキャン出力セルは「出力禁止」状態となっているためです。もちろん、実際にはN側の端子からはP側とは逆の信号が出ているので通常動作は行えています。

図2 LVDSのN側端子が入力として見える理由

このため、N側の端子はP側に出力したものとは逆の電圧が入力として見えるというわけです。また、ZYNQの場合ではEXTESTモードで無理やりP側と同じ電圧をN側から出力しようとしても、出力に設定はできますが、無視されます。N側の出力セルは効果を持ちません。

入力に設定した場合

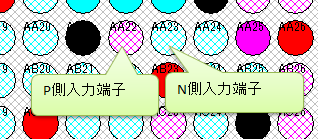

LVDSで入力にコンフィグした端子は、バウンダリスキャンでは普通にPとNの電圧が逆位相で見えます。

図3 LVDSの入力端子を見た場合

しかし、P側端子とN側端子を直結して同電位とした場合でも、実際にはわずかな違いによってN != Pとして見えてしまいます。同時に'0'または同時に'1'として見えることはほとんど※ありません。

※入力信号の遷移とTCKの遷移が偶然重なったときにN!=Pとなる場合が観測されると思われる

また、入力専用として作られた端子をバウンダリスキャンによって出力にすることはできません。入力専用として作られた端子は、配置配線されたときに出力バッファがディゼーブルになるものと考えられます。

図4 LVDSの入力端子を見た場合

基板検査に関するノウハウ

未コンフィグのとき

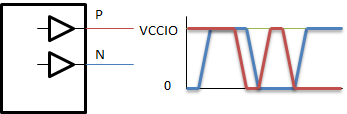

コンフィグされてれいなFPGAでは、I/OはLVDSにはなりません。P側またはN側端子をバウンダリスキャンで自由に操作できますが、電源電圧いっぱいまで振れてしまいます。

図5 未コンフィグのFPGAでは自由に電圧を設定できるが、VCCIOまで振れてしまう

コンフィグされたFPGA

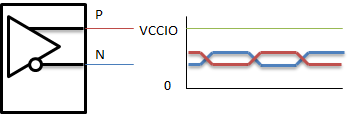

コンフィグされたFPGAでは、LVDSとして論理合成・配置配線したI/OはLVDSにはなります。P側端子のみ自由に操作でき、N側端子はP側と反対の信号を出します。振幅はLVDSなどの差動規格で定められたものになります。

図6 コンフィグ済のFPGAではN側は自由に動かせないが、LVDS規格の信号になる

基板検査を行うには

FPGAをコンフィグしてしまうと、N側が自由に動かせません。FPGAをコンフィグしなければP側もN側も自由に動かせますが、電圧規格がLVDSになりません。

このようなジレンマがありますが、基本的に基板検査はFPGAは未コンフィグの状態で行ったほうがよいでしょう。

まとめ

以上の検証から得られるノウハウは3つあります。

(1) LVDSにするとN側の出力は操作できない

(2) 入力専用にした端子は出力セルが操作できない

(3) 基板の導通検査を行うには、FPGAは未コンフィグの状態で行ったほうがよい

図8 LVDS信号の出力と、入力

(なひ)