MITOUJTAGとは何か

製品について

ご購入を検討中の方へ

サポート

JTAGについて

JTAG技術サービス(有料)

JTAG開発日記

JTAGを熱く語る

高速トランシーバのEXTEST

高速トランシーバの配線をテストするため、IEEE1149.6という規格があります。

IEEE1149.6では、EXTESTの代わりに、EXTEST_PULSEとEXTEST_TRAINという2つの新しいコマンドが追加されました。

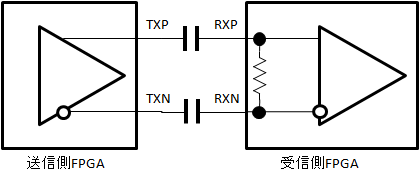

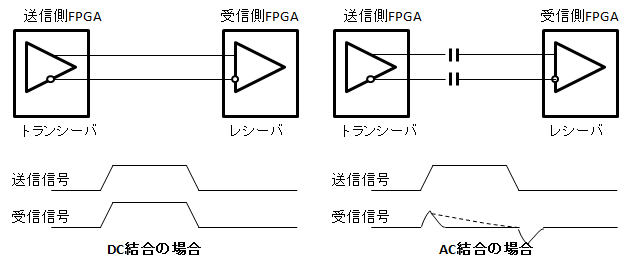

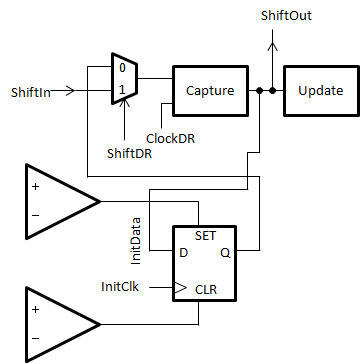

普通、高速差動配線には下の図のようにコンデンサで結合されています。これゆえ、当初のJTAG規格IEEE1149.1では検査ができませんでした。

図1 高速差動配線にはコンデンサが入る

まずは普通にGTXをEXTESTしてみる

本当に検査ができないのか、実際にどうなるのかやってみましょう。

写真1 高速トランシーバの出力コネクタをオシロで見る

XILINX 7シリーズでは、GTXのポートがEXTESTで操作できるようになっています。

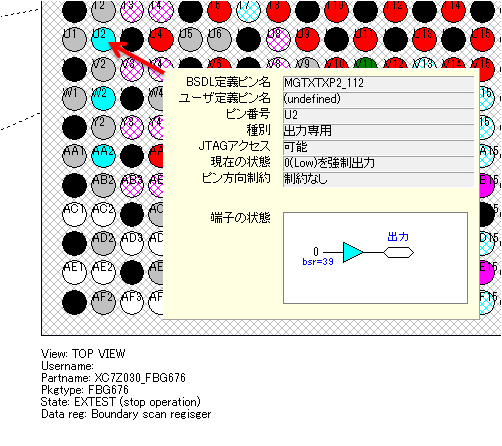

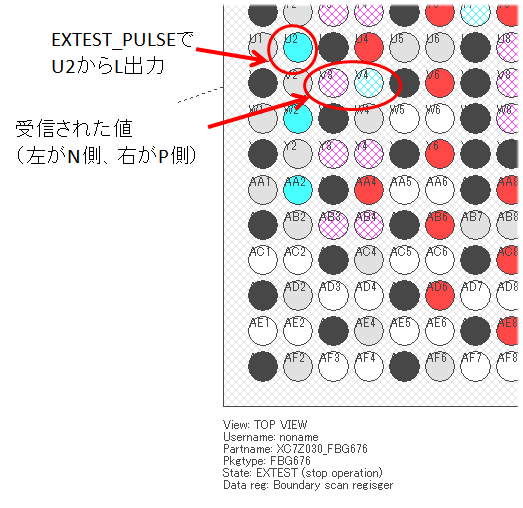

下の図のU2という端子は、XC7Z030FGG656のMGTTXTXP2、つまりGTXのCH2のTXのP側です。その左側に位置するU1番の端子が対になるTXNです。残念ながらTXNはバウンダリスキャンできないようです。

図2 ZYNQのU2番ピンはMGTのP側

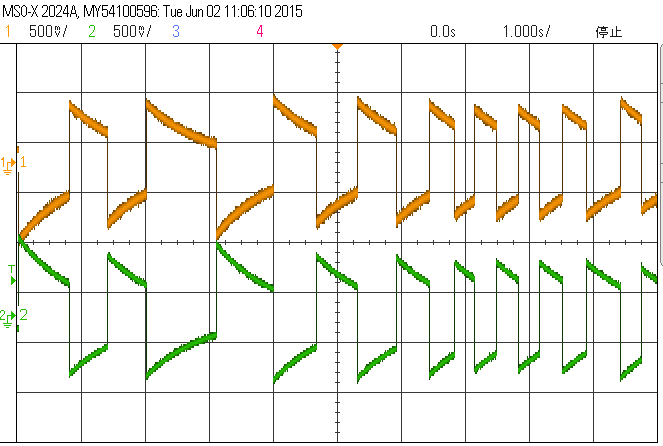

普通にEXTESTコマンドを発行して、バウンダリスキャンでカチカチしてみました。

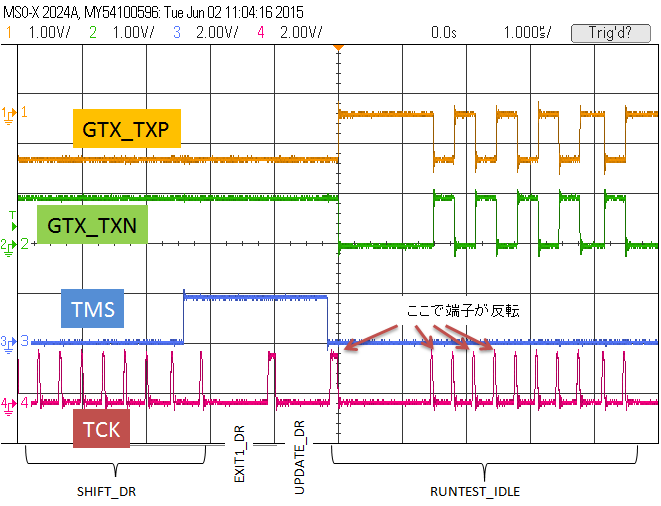

図3 GTXの端子をEXTESTすると・・

P側とN側の端子が逆位相で動くのが確認されました。横方向の1divは1秒なので、マウスクリックの速度です。波形が減衰しているように見えるのは、下の図のように、FPGAとコネクタとの間にコンデンサが入っているためです。

上の波形を見てみると、変化したときには+Vですが、しばらく経つと0Vに向かって減衰していきます。次のトグル時には-Vになります。このように、コンデンサが入ると時間とともに変化するアナログ的な信号になってしまいます。

EXTEST_PULSEとEXTEST_TRAIN

IEEE1149.6ではEXTEST_PULSEとEXTEST_TRAINという命令が追加されました。

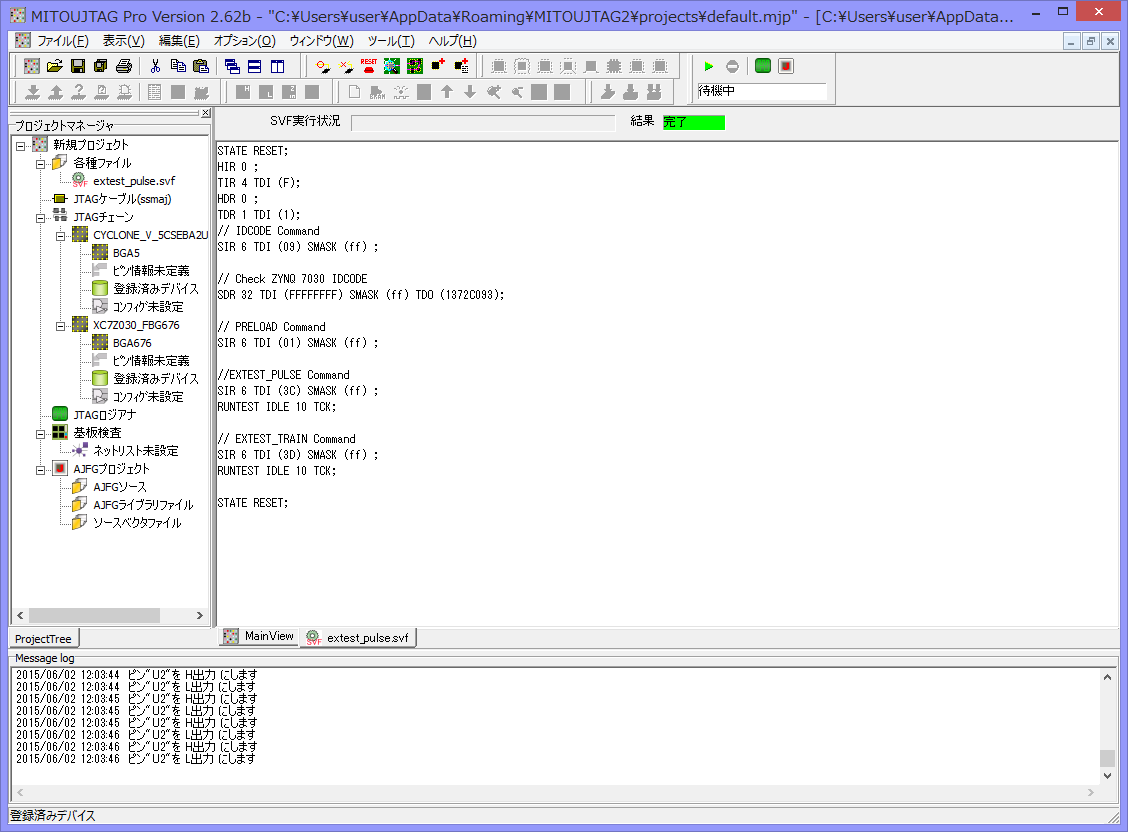

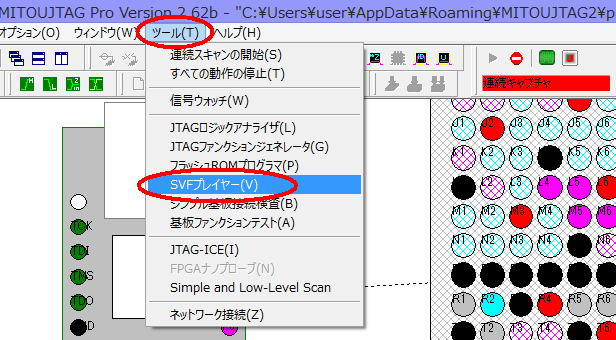

ZYNQでも実際にやってみましょう。MITOUJTAGで、このようなJTAGの実験を行うには、SVFプレイヤーを使うのが便利です。

SVFプレイヤーの起動とコマンドの記述

メインメニューから、ツール→SVFプレイヤーと操作すれば、SVFプレイヤーが起動します。

図4 SVFプレイヤーの起動

SVFプレイヤーが起動したら、真っ白な画面が出ますので、そこにSVFコマンドを記述していきます。

図5 SVFコマンドの記述

書いたコマンドは以下のようなものです。簡単に解説すると、ZYNQはARMのコアとFPGA部分が直列につながっているので、TIRとTDRを設定しています。

STATE RESET; HIR 0 ; TIR 4 TDI (F); // ARMコアに1111(BYPASS)コマンドを常に与える HDR 0 ; TDR 1 TDI (1); // ARMコアのデータレジスタは常に1bitの1 // IDCODE Command SIR 6 TDI (09) SMASK (ff) ; // Check ZYNQ 7030 IDCODE SDR 32 TDI (FFFFFFFF) SMASK (ff) TDO (1372C093); // PRELOAD Command SIR 6 TDI (01) SMASK (ff) ; //EXTEST_PULSE Command SIR 6 TDI (3C) SMASK (ff) ; RUNTEST IDLE 10 TCK; // EXTEST_TRAIN Command SIR 6 TDI (3D) SMASK (ff) ; RUNTEST IDLE 10 TCK; STATE RESET;

その後、ZYNQの030のIDCODEが1372C093であることを確認しています。インフラストラクチャテストです。

それから、PRELOADを行ってバウンダリスキャンレジスタに現在の値を取り込んでおきます。こうしないと、EXTESTの時に危険な値が出てしまうためです。

そして、ついにコマンド3CのEXTEST_PULSEと、コマンド3DのEXTEST_TRAINを与えています。

この2つのコマンドは何をするのか?

EXTEST_PULSEとEXTEST_TRAINは、どちらもEXTESTと同じく、UPDATE_DRステートでI/Oピンからバウンダリスキャンレジスタの値を出力します。

図6 EXTEST_TRAINとEXTEST_PULSEの動作

しかし、EXTEST_PULSEはRUNTEST_IDLEステートに入ったときに、データを反転します。EXTEST_TRAINはRUNTEST_IDLEステートでTCKを受けるたびに、データをトグルします。

図6 EXTEST_TRAINとEXTEST_PULSEの動作

実際の波形

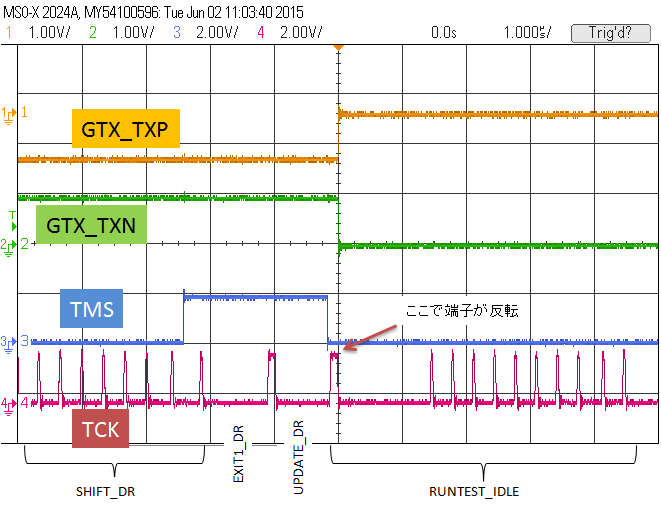

下の図は、実際にZYNQでEXTEST_TRAINを実行したときのものです。RUNTEST_IDLEステートに戻った後、最初のTCKの立下りで、TXPとTXNの端子が反転していることがわかります。

図8 EXTEST_PULSEの動作波形(クリックで拡大)

次はEXTEST_TRAINの波形です。RUNTEST_IDLEに戻った後、TCKのパルスがくるたびに端子が反転していることがわかります。

図9 EXTEST_TRAINの動作波形(クリックで拡大)

確かに、想定どおりの波形が出ました。

このように、EXTEST_PULSEとEXTEST_TRAINを使うと、TCKの2分の1の速度で高速トランシーバからトグル波形を出すことができるので、コンデンサの影響を受けずに信号を受信側へと送ることができます。

受信側の動作

EXTEST_PULSEを使うと、高速差動ドライバからパルスが出力されることがわかりました。これを受信するにはどうすればよいでしょうか。

ポイントは3つです。

- トランシーバとレシーバはコンデンサで結合されている(AC結合)かもしれないし、直結されている(DC結合)かもしれない。

- LVDSなど、オフセット電圧がどのくらいあるかわからない。どのくらいあっても良いようにしたい。

- 差動信号を片側ずつ検査したい。

AC結合とDC結合

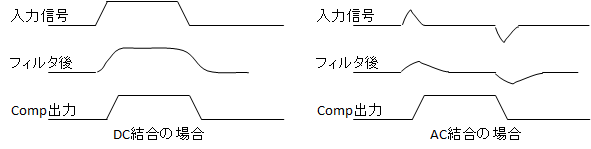

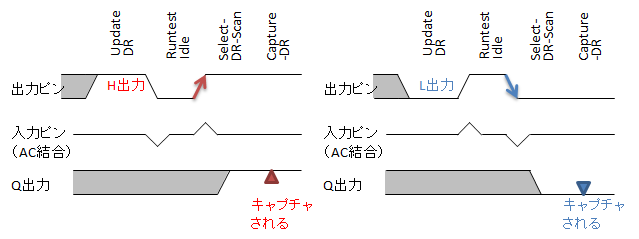

例えば、Hを出力しようとしたとき、H→L→Hというパルスとなって出力されます。 このパルスはDC結合されていればそのままの形状で、コンデンサで結合(AC結合)されていれば、微分波形となって伝わります。(時定数に対して速度が十分に遅ければ点線のような波形となる)

図10 AC結合とDC結合

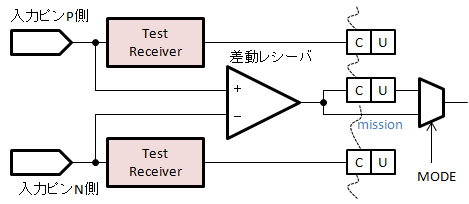

受信側のI/Oピンには、このエッジを受信するためテストレシーバという回路が入っています。

図11 差動信号の受信端子の構成

テストレシーバは、差動ペアの両方の端子に入っています。差動ペアに対して1個だけというのではなく、ピンに対して1個ずつ入っています。

それゆえ、受信ペアには差動レシーバは2個あります。このレシーバはEXTEST_PULSEまたはEXTEST_TRAINモード(AC TESTモードという)のとき有効になります。有効になった場合、レベルではなくエッジに反応するようになります。

なお、テストレシーバが有効になるのは、ACテストモードのみです。通常のEXTESTモードではレベルを検知するDCテストモードになります。

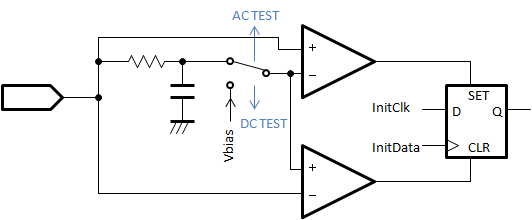

テストレシーバの構造

テストレシーバは以下のような構造をしています。

図12 テストレシーバの構造

入力された信号をCとR(LPFを構成)で遅延させて、元の入力信号との差をコンパレータで比較します。コンパレータにはヒステリシスがかかっています。

入力信号が変化したら、それに合わせてフリップフロップをセットまたはクリアするので、DC結合であっても、AC結合であっても、フリップフロップの出力からは、もともとのトランシーバが出した信号と同じ形状の信号が復元されます。

図13 テストレシーバの入出力波形

InitClkは、以下の条件の信号です。

( (EXTEST_TRAIN or EXTEST_PULSE) and (EXIT1_DR or EXIT2_DR) and TCK ) or ((Capture_DR or EXTEST) and not TCK)

図14 InitClkの生成

これが意味するところは、

- ACテストモードであれば、EXIT*_DRステートのTCKの立ち上がりで

- DCテストモードであれば、Capture_DRステートのTCKの立ち下がりで

でInitDataの値をサンプリングするというこです。

また、InitDataにはJTAGバウンダリスキャンのCapture回路の出力が接続されます。全体の校正は図15のようになります。

※TAPの遷移はCapture→ShiftDR→Exit1DR→UpdateDR→SelectDRまたはRuntestIdleなので、ACテストモードではCapture回路は現在の値を初期値として保持しているといえる。

図15 CaptureDRの部分の構成

テストレシーバの動作

すなわち、ACテストモードでH出力した場合、

- EXTEST_PULSEでHを出力すると、端子からはH→L→Hが出力される

- 入力の波形が立ち上がるとSETがHになって、QはHになる

- Capture回路は、そのHをサンプリングする

という動作をします。

Lを出力した場合、

- EXTEST_PULSEでLを出力すると、端子からはL→H→Lが出力される

- 入力端子波形が立ち下がるとCLRがHになって、QはLになる

- Capture回路は、そのLをサンプリングする

という動作をします。

図16 Updateで出力した値が、入力でキャプチャされるしくみ

AC結合でもDC結合でも、H出力でもL出力でも、EXTEST_PULSEで出力した値がCaptureされるというわけです。

実験

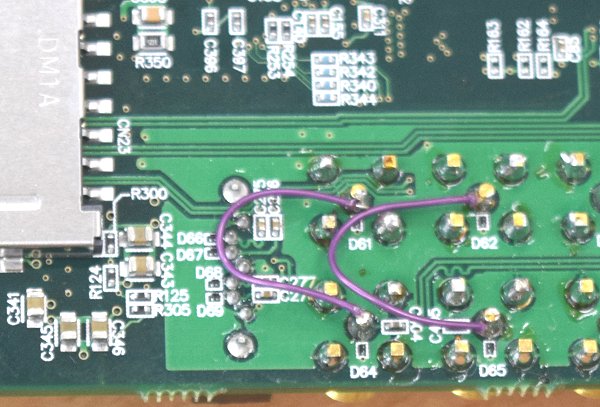

実際に実験してみることにしました。まずはGTXのTXP2とRXP2、TXN2とRXN2をジャンパでつぎます。

写真2 GTXのTXとRXをジャンパする

これをMITOUJTAGでスキャンしてみましょう。ただし、現在のMITOUJTAG (V2.6)はEXTEST_PULSEに対応していません。そこで、BSDLファイルを無理やり書き換えることにで実験しました。

まずは、使用しているデバイスのBSDLファイル xc7z030_fbg676x.bsd を開きます。

1077行目付近に

"EXTEST (100110)," & -- BOUNDARY

"SAMPLE (000001)," & -- BOUNDARY

"PRELOAD (000001)," & -- Same as SAMPLE

"USERCODE (001000)," & -- DEVICE_ID

"HIGHZ (001010)," & -- BYPASS

"EXTEST_PULSE (111100)," & -- BOUNDARY

"EXTEST_TRAIN (111101)," & -- BOUNDARY

という箇所があるので、

"EXTEST_PULSE (100110)," & -- BOUNDARY

"SAMPLE (000001)," & -- BOUNDARY

"PRELOAD (000001)," & -- Same as SAMPLE

"USERCODE (001000)," & -- DEVICE_ID

"HIGHZ (001010)," & -- BYPASS

"EXTEST (111100)," & -- BOUNDARY

"EXTEST_TRAIN (111101)," & -- BOUNDARY

に書き換えます。無理やりEXTESTとEXTEST_PULSEを入れ替えてしまおうというわけです。

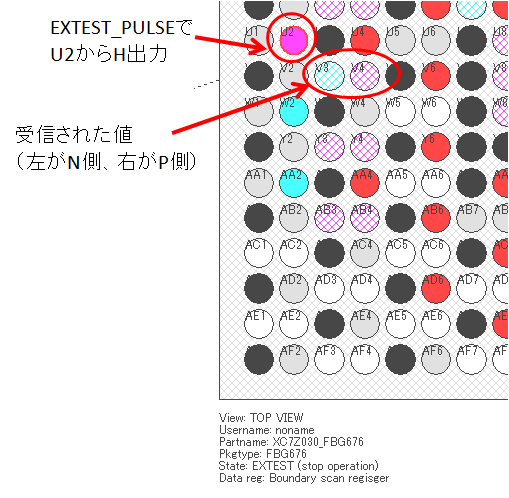

そして、バウンダリスキャンをやってみます。

まずはH出力してみました。

図17 EXTEST_PULSEでH出力すると、Hが入力される

次はL出力です。

図18 EXTEST_PULSEでL出力すると、Lが入力される

このように、H出力すると、受信したピンからもHが、L出力すると受信ピンからもLがキャプチャできることがわかります。

タイミングの問題

ただし、N側のピンは実際にはバタバタと遷移しました。FPGA内のテストレシーバに仕掛けられたコンデンサや抵抗の時定数に依存するところが大きいので、タイミング的な問題も相当にあるのでしょう。BSDLファイルのWarningには

"The IEEE Std 1149.6 EXTEST_PULSE and EXTEST_TRAIN instructions" & "require a minimum TCK freq of 15 MHz and min temp of 0C." &

と書かれているのも気になるところです。

まとめ

- EXTEST_PULSEを使うと端子から「値」ではなく「パルス」が出力されます。

- 受信側のテストレシーバにはパルスを検出する仕組みがはいっていて、AC結合、DC結合に関わらず、EXTEST_PULSEで出した値が読めるようになっています。

- XILINXでは7シリーズ以降でこのIEEE1149.6の仕組みが入っています。