製品情報

- MITOUJTAG

- JTAG書き込みツール

- IC真贋判定サービス

- Spartan-7評価ボード

- Artix-7評価ボード

- ZYNQ搭載ADCボード「Cosmo-Z」

- Cosmo-Zについて

- 2017年度アップグレード

- ライブラリAPIマニュアル

- このような用途に最適

- ボード写真

- Type-C基板

- 仕様と機能

- チュートリアル

- 使用方法

- ダウンロード

- 注文情報

- その他

- 開発者向け情報

- 内部構造

- 内部レジスタ

- ZynqでLinuxが動くまでのまとめ

- 開発環境の準備

- EMIOの設定

- メモリの設定

- AXIポートの設定

- 割り込み発生

- XILINXソフトウェア開発環境の準備

- u-bootの生成

- ramdiskの生成

- linuxの生成

- DeviceTreeの生成

- Linuxのカスタマイズ

- ToDo

- 古い情報

- 開発日記

- 2017年10月

- 2017年9月

- 2017年8月

- 2017年7月

- 2017年6月

- 2017年5月

- 2017年4月

- 2017年3月

- 2017年2月

- 2017年1月

- 2016年12月

- 2016年11月

- 2016年10月

- 2016年9月

- 2016年8月

- 2016年7月

- 2016年6月

- 2016年5月

- 2016年4月

- 2016年3月

- 2016年2月

- 2016年1月

- 2015年12月

- 2015年11月

- 2015年10月

- 2015年9月

- 2015年8月

- 2015年7月

- 2015年6月

- 2015年5月

- 2015年4月

- 2015年3月

- 2015年2月

- 2015年1月

- 2014年12月

- 2014年11月

- 2014年10月

- 2014年9月

- 2014年8月

- 2014年7月

- 2014年4月

- Kintex-7 PCIe Express光ボード「Cosmo-K」

- 販売終了製品

- Spartan-6評価ボード

- EXPARTAN-6T

- 18bit20chデータロガー「AD360」

- Kintex-7 HDMI&CSIボード「Cosmo-K DVI」

- 1Gサンプリング超高速ADCボード「HyperFADC」

- MPPCアレイ

- 18bit AD変換ボード

- FPGA拡張ベースボード

- 究極のRX62N評価ボード

- 特電FX3評価ボード

- RXDuinoライブラリ

- 仕様と機能

- RXduinoダウンロード

- 注文情報

- セットアップガイド

- 使用例

- RaXinoのLEDを点滅させる

- LEDをPWM点滅させる

- RX-MEGAにMARY-GBを載せてGPSを受信する

- ルネサスE1エミュレータを利用したデバッグ

- RXduinoライブラリでUSB通信を行う

- 特電HALでUSB通信を行う

- RXduinoライブラリでUARTとUSB仮想シリアルを使う

- Nahimonによるプログラムのロード

- 複数のシリアルを使う

- 12ビットA/Dコンバータを使う

- サンプルコード集

- 基本のプログラム

- 基本のLEDチカチカ

- PWMでLEDをじわーっと光らせる

- 12bit A/Dコンバータのサンプル

- セルフリセット

- GPIOのテスト

- アナログ波形の出力

- 浮動小数点演算とprintf

- 内蔵データフラッシュの使い方

- ピン割り込みの使い方

- タイマ割り込みの使い方

- PWMの周波数を変更する

- RTCの使い方

- サーボを20チャネルとPWMを14チャネル使う

- ステッピングモータのテスト

- シリアル通信とUSB

- USB仮想COMポートを用いた通信

- シリアルポートを用いた通信

- 複数のシリアルポートを使うプログラム

- シリアル通信のCR(0x0d)やLF(0x0a)の設定

- シリアル通信のストップビットモードなどの変更

- SDカード(MMCカード)の動作サンプル

- USBホストとしての動作とエニュメレーション

- AndroidスマートフォンとADBで通信する

- ネットワーク機能

- HTTPクライアント ホームページの閲覧

- イーサネットのパケットキャプチャ

- UDPの送受信

- メールを送信する

- Twitterにつぶやく

- TELNETでどこかにリモートログインする

- TELNETデーモン

- NTPで内蔵時計を合わせる

- 各種部品との接続

- RaXinoに搭載されている加速度センサ

- キャラクタ液晶に文字を表示するには

- 秋月電子のジャイロと接続する

- フラクタルの描画

- 3軸加速度センサ KXM52を使う

- マルツのOLEDを使う

- MARY-GBを用いたGPSの受信

- RXduinoマニュアル

- RaXino(ラクシーノ)

- RaXino-i(ラクシーノ・アイ)

- RX-MEGA 某誌付録RX62N用拡張ボード

- JTAG WARP9

- 特電PCI Express評価ボード

技術情報

会社情報

- 会社概要

- 商品のご購入について

- 求人情報

- イベント案内

- FPGAカンファレンス2026出展のご案内

- 展示会DSF2025出展のご案内

- MITOUJTAG Free版のご案内

- 書籍のご案内

- DSF2024出展のお知らせ

- 未踏会議2024出展のお知らせ

- ネプコンジャパン2022出展のお知らせ

- SEMIジャパン2022出展のお知らせ

- FPGAセミナー(初級編)

- FPGAセミナー(中級編)

- Cosmo-Z活用セミナー

- Trenz社製品活用ZYNQセミナー

- 日本物理学会2018春季

- 日本物理学会2018春季

- 応用物理学会2018春季

- 応用物理学会2018春季

- 応用物理学会2018春季

- FPGAカンファレンス2018

- Cosmo-Zセミナー

- ZYNQ&Trenz製品セミナー

- ET/IoT2017

- 2017年春の学会付設展示会

- Embedded Technology 2016

- 応用物理学会2016春季

- Embedded Technology 2015

- JSAP EXPO AUTUMN 2015

- 物理学会第70回年次大会

- JSAP EXPO SPRING 2015

- MITOUJTAG講習会

- ET2014

- ET2013

- ET2012

- ET2011

- ET2010

- ET2009

- ET2008

- ET2006

- ET2005

- FPGAカンファレンス2007

- FPGAカンファレンス2008

- FPGAカンファレンス2009

- ボードコンピュータ展2008

- IPAX2007

- IPAX2008

- IPAX2009

- テクノフロンティア2009

- ESEC2007

- EDSFair2009

- EDSFair2010

- FPGAカンファレンス2009

- ルネサスRXセミナ2012

- Interface誌2012年1月号 特設ページ

- CEATEC2011

- CEATEC2012

- 特殊電子回路の通信簿

FPGAの設計

FPGAの設計について

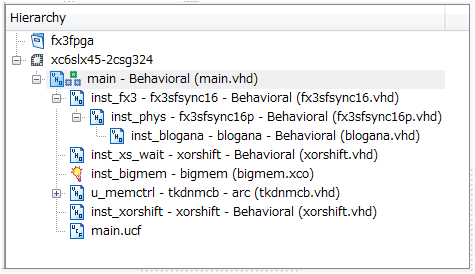

特電が提供するFPGAのサンプルデザインは、次のような構造になっています。

main.vhdがメインのモジュールです。

fx3sfsync16.vhdとfx3sfsync16p.vhdが特電の提供するFX3インタフェース用コアです。

(blogana.vhdは、当社の提供するJTAGデバッグ用コアです。これは削除していただいて構いません。)

IPコアの使い方についてはこちらのページをご覧ください。

xorshiftは、テスト用の乱数発生回路です。また、検証用にランダムなタイミングのWAITを発生させるためにも用いています。

bigmemは、128kBのメモリ(BlockRAM)です。

tkdnmcb.vhdは、MCBをカプセル化したメモリコントローラで、Spartan-6ボード上のDDR2 SDRAMにアクセスするために使います。

main.ucfはピン配置などの制約ファイルです。

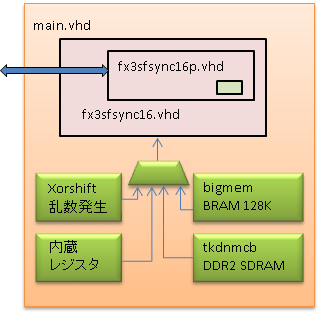

これらのモジュールの関係を図示すると次の図のようになります。

USBに対してデータを送信するモジュール(IN転送時のデータソース)は、XorShift、内蔵レジスタ、BigMem、tkdnmcbの4種類です。これらのどのモジュールが使われるかは、flag[1:0]によって選択されます。

各モジュールについて

Xorshiftは、32bitの乱数を発生させる回路です。1回の演算で32bit単位で出てくるので使いやすく、また、乱数の周期は2^128と長いのが特徴です。

内蔵レジスタは、32bit×16本のレジスタセットです。VHDL上でireg0〜ireg15というレジスタがそれです。このレジスタには機能は割り当てられておらず、書き込まれた値を保持して読み出せるようにしているだけです。このレジスタはお客様のユーザデザインで何らかの機能を持ったレジスタを作る際のひながたとして用意しています。

tkdnmcbは、Spartan-6基板上のDDR2 SDRAMにアクセスするためのコアです。DDR2 SDRAMにクロック200MHz(データレートは400MB/sec)でアクセスします。MCBのポート0をUSB用に使用しています。残りのポートは未使用なので、データキャプチャやCMOSイメージセンサなどをつなぐ際のひな形としてご利用ください。

bigmemは、CoreGenで生成したBlockRAMです。内蔵BRAMにアクセスする際のひながたとしてご利用ください。

IPコアの使い方についてはこちらのページをご覧ください。

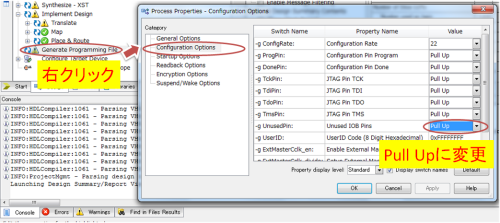

論理合成時の注意

ISEで論理合成する際に、Generate Programming Fileで右クリックし、Configuration Optionsのプロパティを出し、Unused IOB PinsをPull Upに必ず変更してください。

Copyright(C) 2012-2013 TokushuDenshiKairo Inc. All rights reserved.