開発日記

Data2Memが動かないのでROM化ができない

2020/2/4

MicroBlazeのデータをROM化するにはdata2memというユーティリティを使います。

data2memはexeファイルで与えるのではなく、vivadoのtclコンソールや、XSDKのxsct、Vivado HLS Tcl Shellなどから起動します。

使い方は、

data2mem -bm vivado/vivado.runs/design_1_wrapper_bd.bmm -bt vivado/vivado.runs/impl_1/design_1_wrapper.bit -bd ../sdk/spi/Debug/spi.elf tag microblaze_0 -o b download.bit

です。

ただ、これを実行しても

ERROR:Data2MEM:4 - Unrecognized device type in .bit file, '7s50csga324'.

と出てしまいます。

Vivado 2018.3や2019.1のXSDKには7s50の情報が入っていないようです。

MicroBlazeてんこもりサンプルの出来上がり

2020/2/4

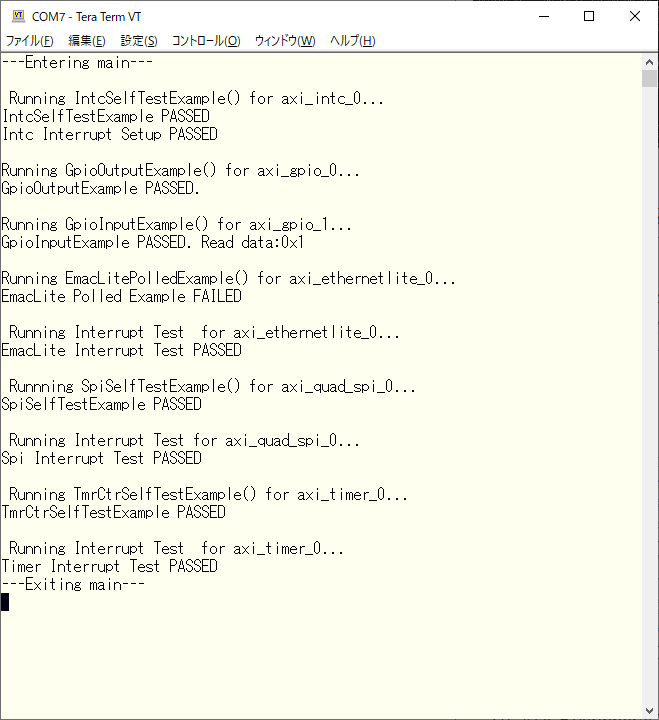

Spartan-7用MicroBlazeのサンプルプロジェクトが出来上がりました。

AXI QSPIというIPを追加しました。

使っているIPは、GPIO、Timer、EthernetLite、QSPI、Uartlite、MIGです。

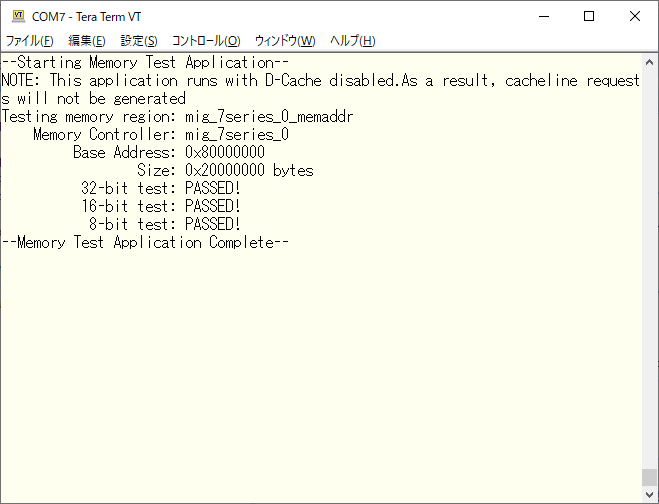

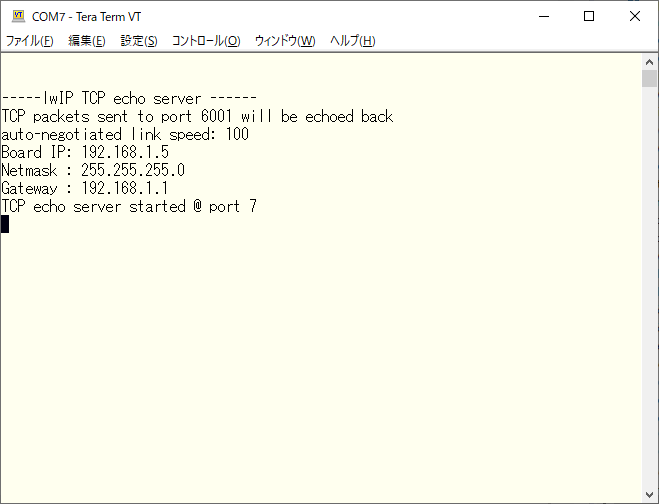

これに対するPeripheral Test、Memory Test、lwIP echoを試しました。

EmacLitePolledExampleはFAILEDになりますが、lwIPのechoではDHCPが取れていて、echoサーバも動いているので、ネットワークの機能にも問題はないのだと思われます。

メモリテストはもちろんPASSです。

下記のURLにSpartan-7 MicroBlazeサンプルを置いておきます。

https://github.com/tokuden/Spartan7/tree/master/microblaze_sample

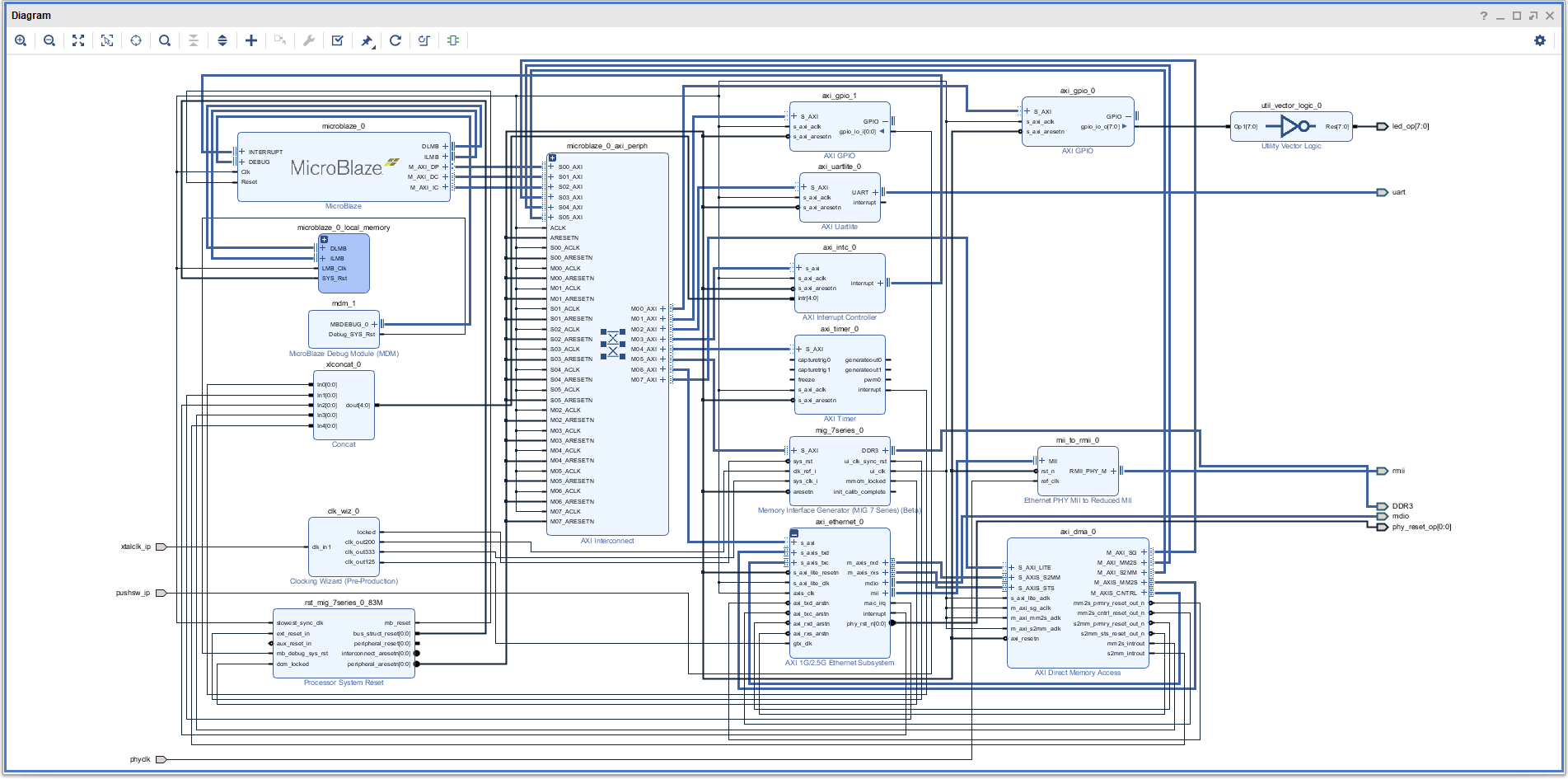

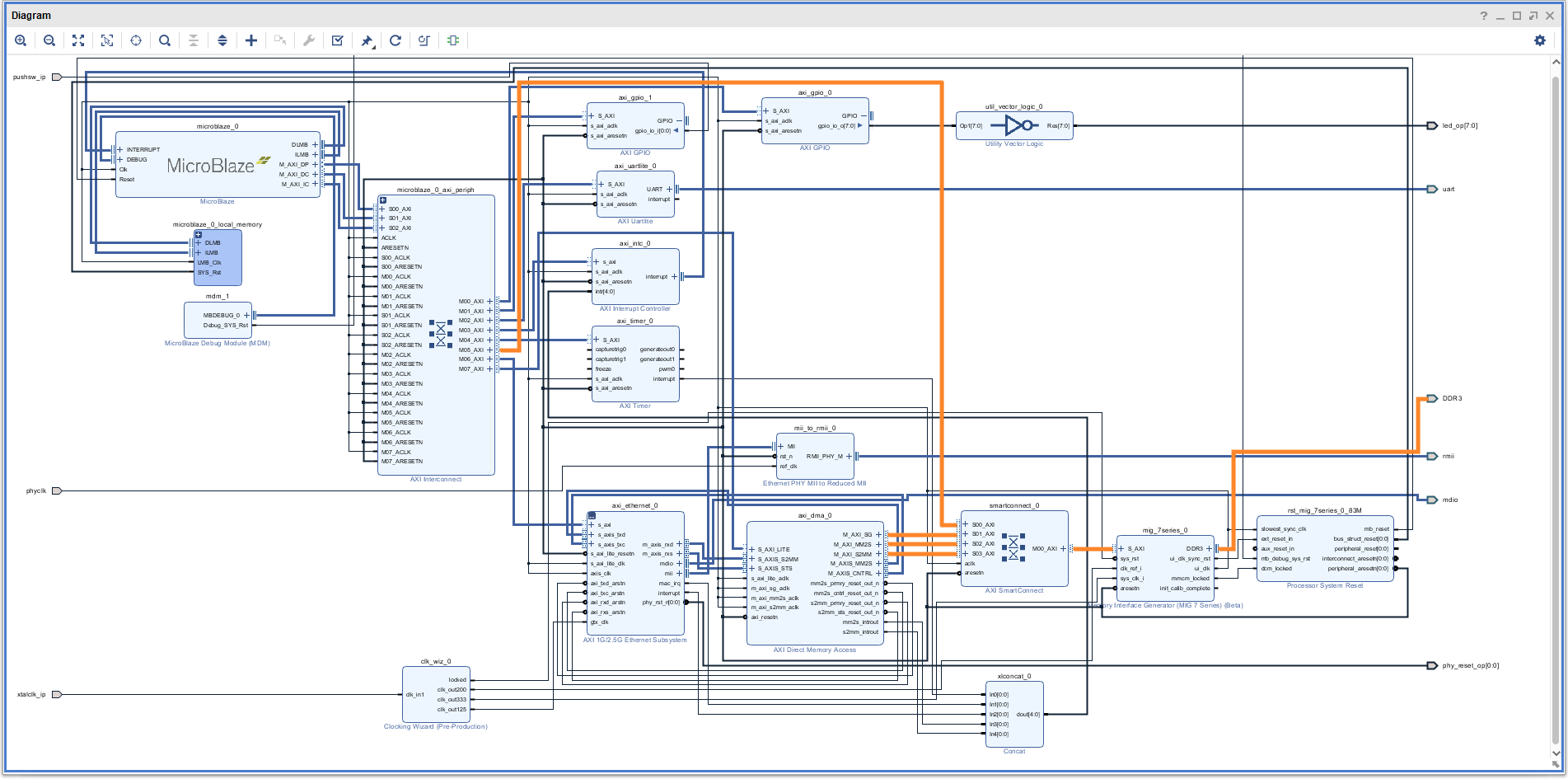

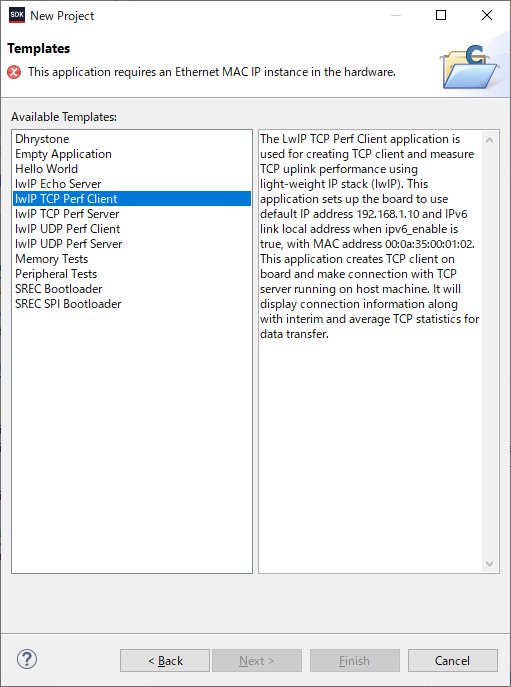

AXI EthernetとDMAを使ったデザインを作ってみる

2020/2/4

XSDKにあるサンプルのPerfテストというのを動かしてみようとすると、Ethernet MAC IPが入っていないとダメだと言ってきます。

いままで使っていたのはEthernetLiteというもので、ここで必要になっているのはEthernetコアで、別物のようです。

EthernetコアはAXI 1G/2.5G Ethernet Subsystemというコアで、これはAXI DMAとセットで使うようです。

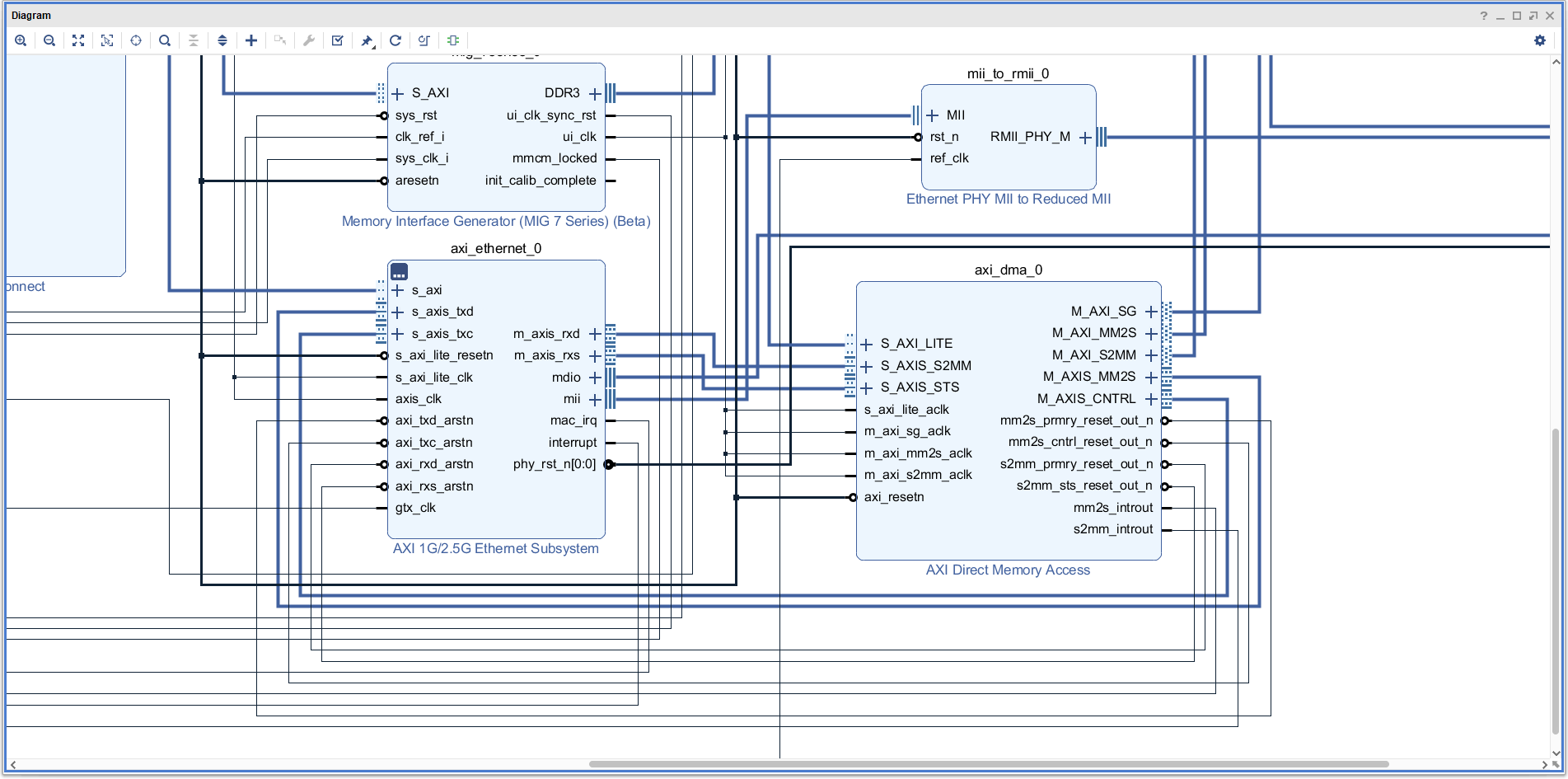

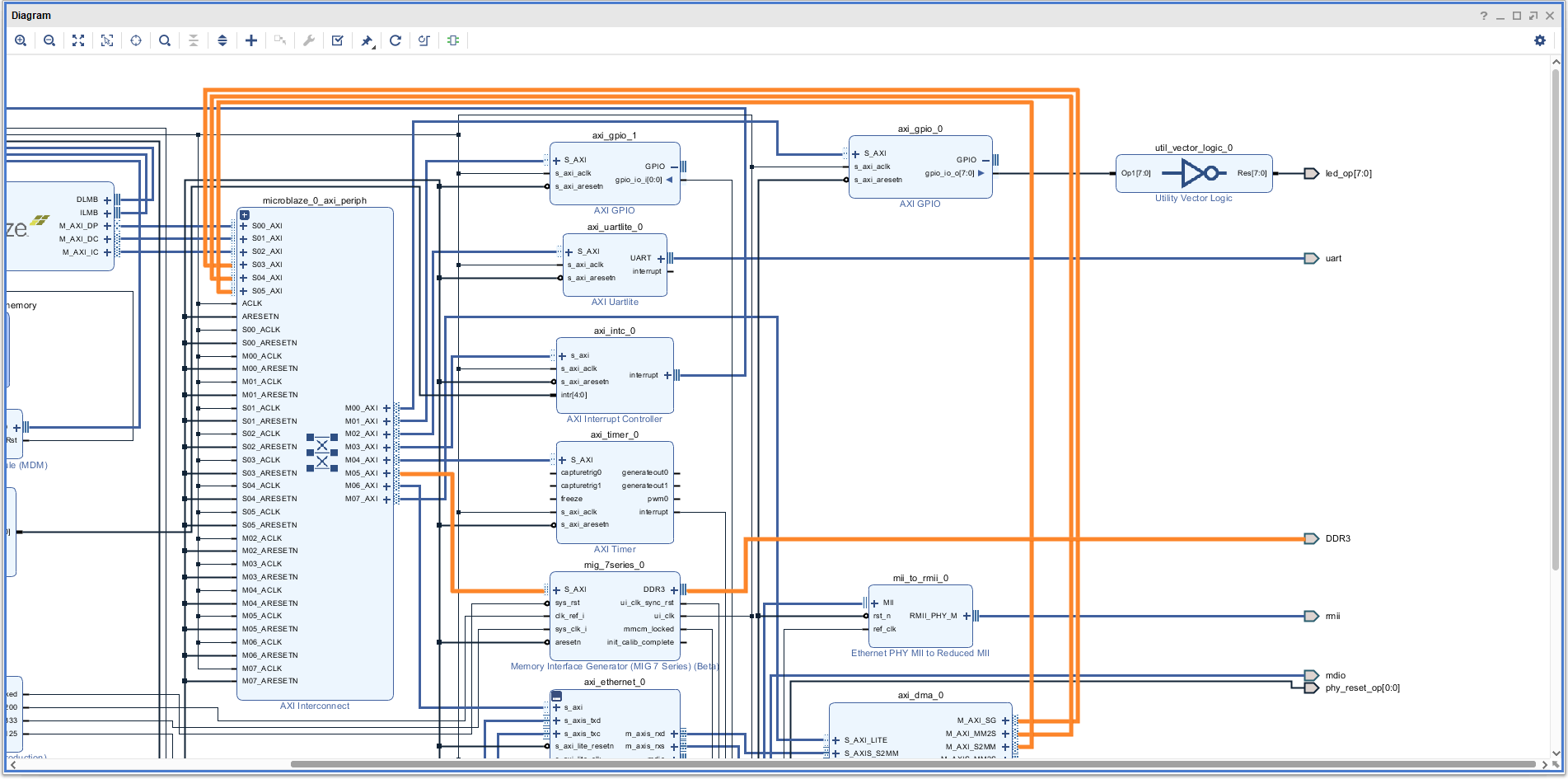

ごちゃごちゃしているので、EtherとDMAのあたりを拡大します。

このデザインがどうなっているかというと、要点は4つです。

- AXI Ethernetの出すrxdとrxcというAXI StreamをDMAのM_AXIS_S2MMとM_AXIS_STSに入れ、DMAコアのM_AXIS_MM2SとM_AXIS_CNTRLをEthernetコアのtxdとtxcにつなぎます。

- DMAコアから4つのリセット信号が出てくるので、mm2s_prmry_reset_outをtxd_arstnに、ctrl_reset_outをtxc_arstnに、s2mm_reset_outをrxd_arstnに、s2mm_sts_reset_outをrxs_resetにそれぞれつなぎます。

- Ethernetコアの出すmac_irq、interrupt、DMAコアのmm2s_introut、s2mm_introutはconcatで束ねてintcにつなぎます。

- DMAコアはM_AXI_SG、M_AXI_MM2S、M_AXI_S2MMの3つのAXIバスを出してきますが、これをSmartConnectで束ねてMIGに送るか、メインのインターコネクトのSlavePort(左側)につなぎます。

このようにぐるっと回して出すか、SmartConnectを使ってDMAコアの出力とメインのインターコネクトからの出力を束ねてMIGに渡します。

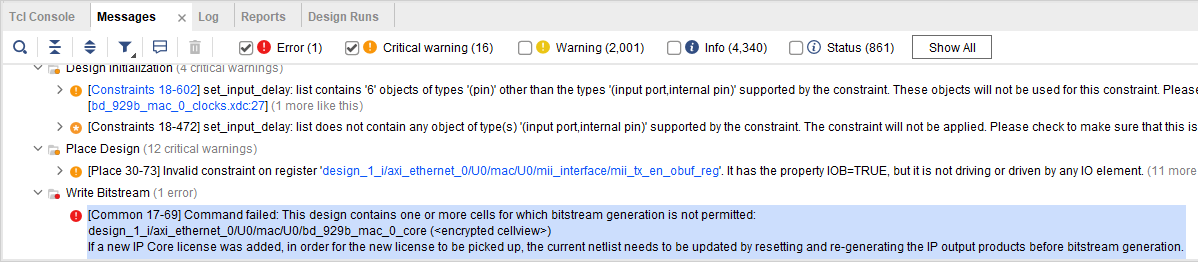

これで設計は問題ないはずなのですが、Generate Bitsteamの段階でbd_929b_mac_0_coreの生成が許可されていないというエラーが出てしまいます。

XILINXのTEMACは、Vivado System Editionか何かを買えば無償で使えるそうなのですが、WebPack Editionではそのままでは使えないような感じです。

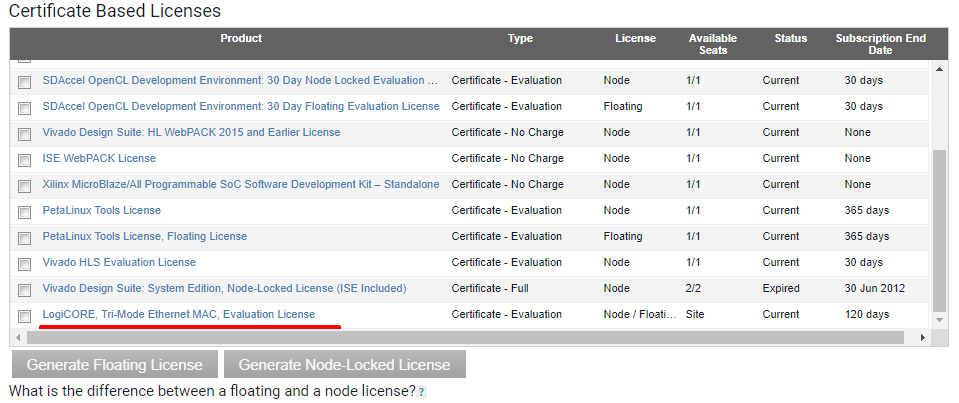

XILINX License Managerからライセンスを取得し、インストールします。

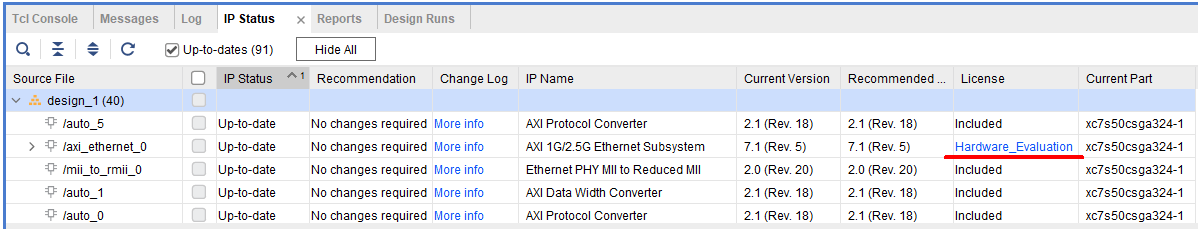

ライセンスをインストールしたら、axi_ethernetのライセンスがHardware Evaluationになります。

一度、Reset Output Productsを行ってから論理合成をします。

これで論理合成はできてBitStreamの生成もできるのですが、残念ながら「何も」動きませんでした。実機にダウンロードしてもHelloWorldさえも動きません。

MicroBlazeがJTAGデバッグに反応しないというエラーが出て、コンソールに何も出てきません。

Hardware Eavaluationのライセンスはコンフィグしてから2~8時間動作するということなので、もしかしたらそのあたりが悪さをして、MicroBlazeが何も動作をしないのかもしれません。

AXI EthernetとAXI DMAを使う案は失敗しましたが、下記のURLにプロジェクトのソースを置いておきます。だれか挑戦してみたい人はどうぞ。

https://github.com/tokuden/Spartan7/tree/axi_ether_dma/microblaze_sample

MicroBlazeでイーサネットが動いた

2020/2/3

MicroBlazeでSpartan-7ボードのイーサネットを動かすことに成功しました。

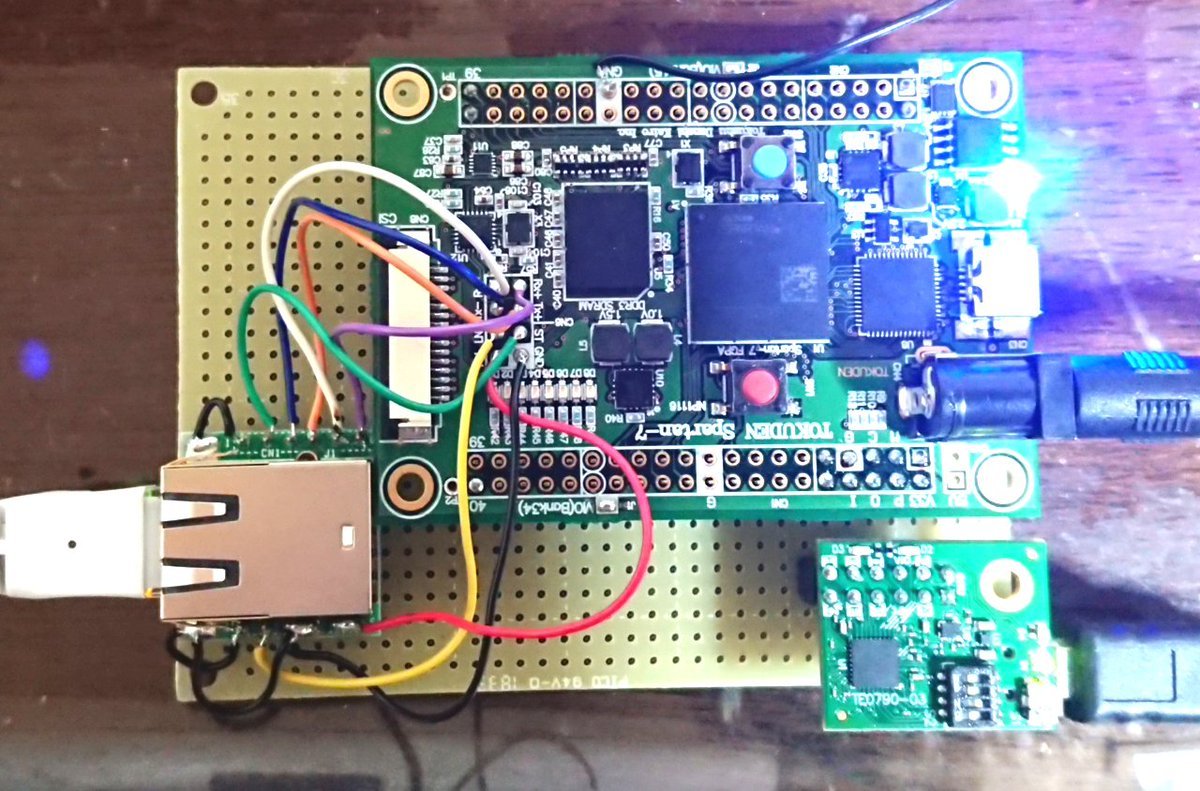

特電Spartan-7ボードにはLANのPHYチップが乗っていて、基板上の8ピンのピンヘッダにTXD+やRXD+などが出ています。ここにパルストランス付きのLANコネクタ(例えば秋月で売っているRJLD-260TC1)をつなぐことでLANが使えるようになります。

本当に直結するだけで動きます。

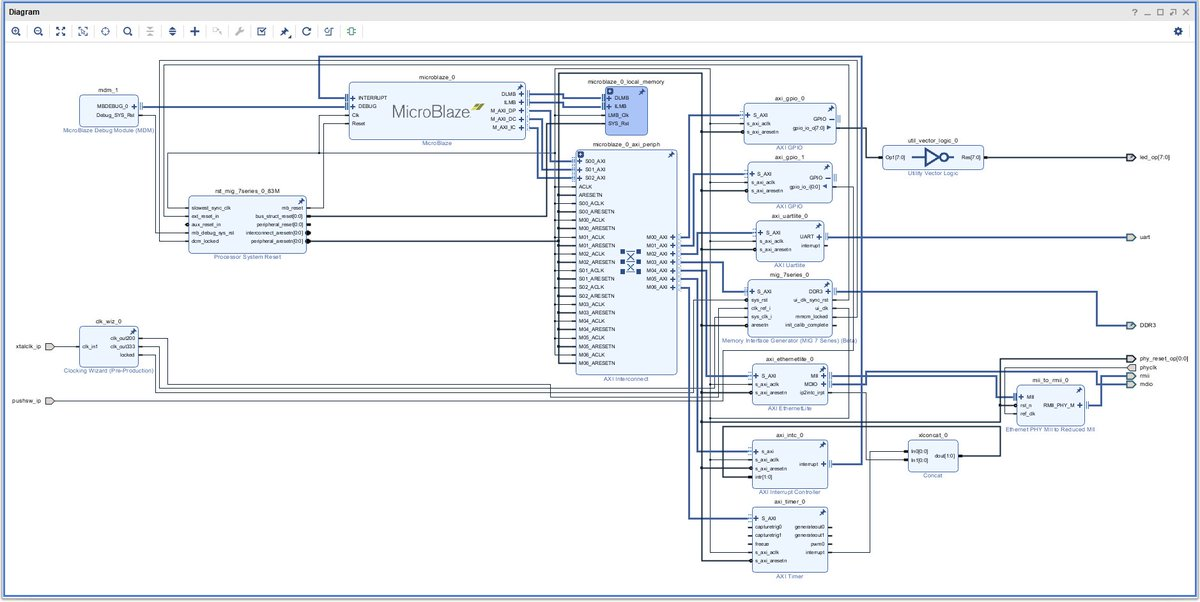

作ったデザインは以下のような感じです。

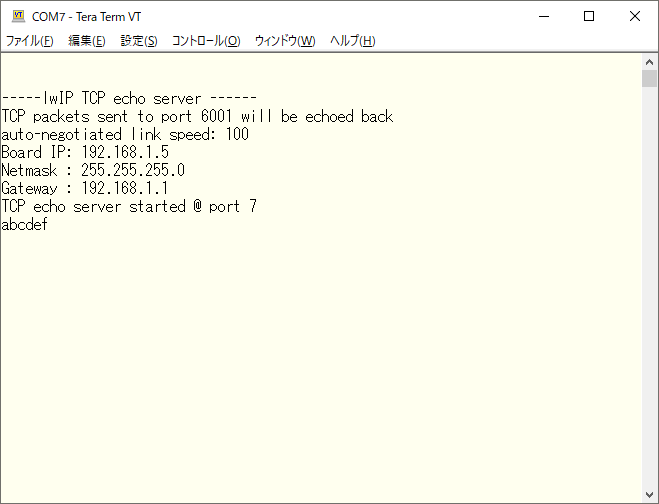

XSDKに含まれているサンプルプロジェクトのひな型を使うのですが、lwIPを使ったエコーサーバを動かします。AXI EthernetLiteのほか、AXI Timerも必要になります。

AXI EthernetLiteとAXI Timerの割込み出力はxlconcatで結合して割込みコントローラに入れます。

PHYに与えるRESETは、内部のaxi_reset_nをそのまま出力すればよいのですが、FPGAがコンフィギュレーションされたときに1回しかLになりません。そのためか、Peripheral Testは最初の1回だけパスします。

こうしてEcho Serverが動くようになりました。

XSDKのEcho serverは全く実用的ではありませんが、DHCPが動く、意外と優れものです。

少なくともLANチップが動作しているかはわかります。

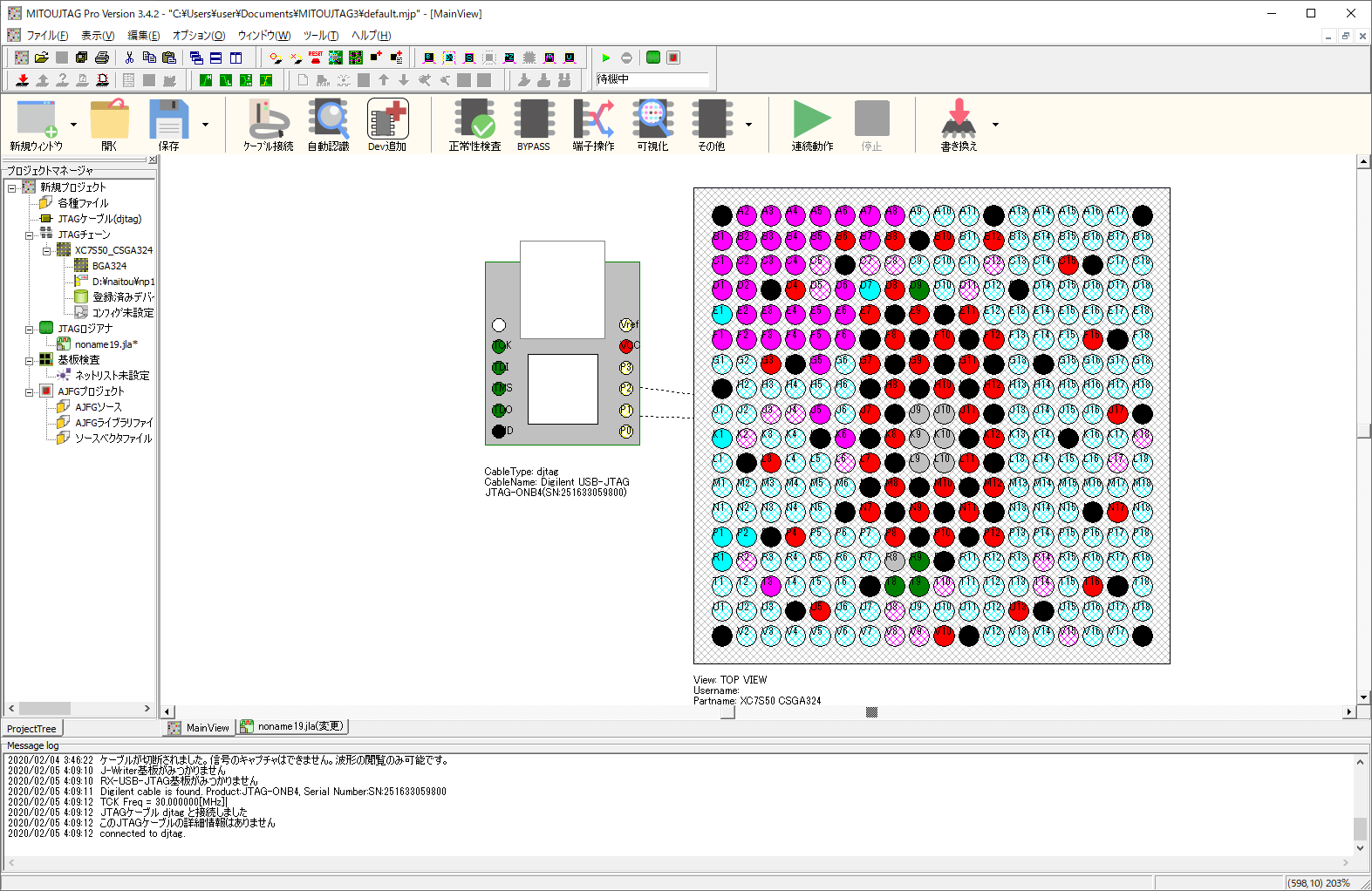

Spartan-7ボードにUSB-JTAGを接続

2020/2/3

このSpartan-7ボードには、LANやSDカードなどIoT機器を構成する様々な要素が乗っています。これらを検査するため、CPUが使えたほうがよいと思われるのでMicroBlazeを入れた実験を行うことにします。

そうすると必要なのは、XILINXのXSDKから認識されるUSB-JTAGと、COMポートとなります。

Spratan-7ボードのUSBはXILIXNのXSDKからは認識されないので、外部に何らかのUSB-JTAGが必要になります。そこで使ったのがTrenzElectronic社のTE0790です。

TE0790はFT2232Hを使ったUSB-JTAGなのですが、Digilent互換のUSB-JTAGとして、Vivadoから認識することができます。非常に小型で、14ピンのコネクタは2.54mmピッチなので、万能基板に乗せて実験することができました。

さらに、TE0790はMITOUJTAGからも認識することができます。

そのため、VivadoやXSDKを使ってデバッグしたり、MITOUJTAGを使って配線チェックしたりすることができる、とてもお得なUSB-JTAGモジュールなのです。

GPIOを順番にテストしていく回路

2020/2/3

特電Spartan-7ボードには64本のI/Oがありますが、I/Oの1本1本から順番に短いHレベルのパルスを出して、それをオシロで確認することでオープンやショートがないかを確認します。

プロジェクトをGithubに上げました。

https://github.com/tokuden/Spartan7/tree/master/gpio_test

もちろん、GPIO検査の結果は正常でした。

今日から開発再開

2020/2/2

1か月ほど受託開発などが忙しく、まったく手が付けられていませんでしたが、今日から久しぶりにSpartan-7ボードの開発を再開します。

発売に向けて一気に進めていきます。

まずは最新のVivado 2019.2で開発して、MicroBlazeを入れてみようと思ったのですが、Vivado 2019.2で生成したハードウェアをexport hardwareしても、hdfファイルが出来なかったので、しばらくは2018.3に戻ることにします。

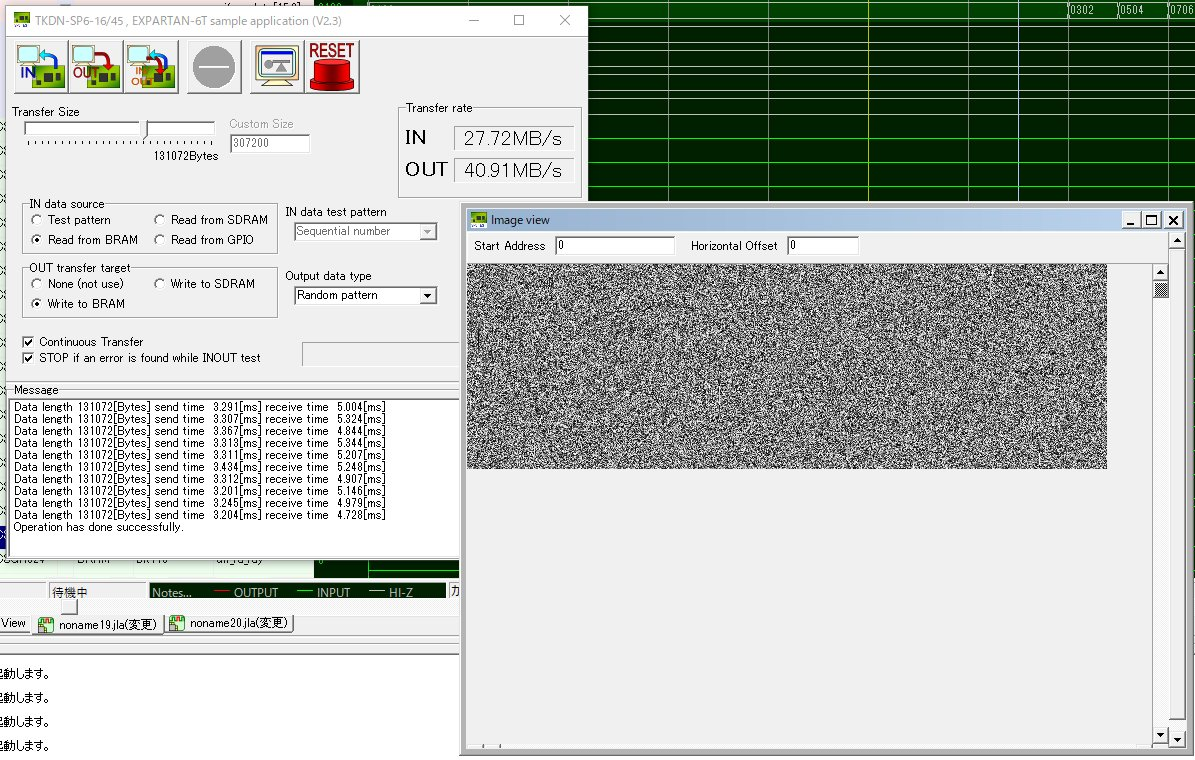

Spartan-7ボードのUSBが動いた

2019/12/31

大晦日もデバッグしています。

Spartan-7ボードでUSB2.0とBlockRAM間の転送に成功した。

久しぶりのVivadoなのでSpartan-6のデザインを移植するだけなのにケアレスミス連発で2日かかってしまいましたが、OUT方向は40MByte/s出ることが確認できました。

IN方向はPCによるけど25~40くらい。次はAXI化するぞ。

Spartan-7ボードのDDR3メモリが動いた

2019.12.28

開発中のSpartan-7ボードでDDR3メモリが動きました。

下の図は、FPGAの端子の状態をモニタしたものです。読み出しと書き込みを周期的に繰り返しています。

どういう回路を作ったかというと、BlockDesignを示します。

このMIGの中身ですが、まず、メモリのクロック周期の選択が3000ps~3300psと、めっちゃ選択範囲が狭いです。

とりあえず3000ps(333MHz)にしておきます。333MHzのクロックということはDDR3は666MHzで動きます。

PHYは4:1にします。

メモリの型番は8bit幅で512MB型のものにするとDDR3メモリの配線がA0~A15まですべて使われます。

次のページ。データバスの幅などを選びますが、特に変更なく64にしておきます。

次にまたクロック速度を指定するところが出ますが、これはMIGのモジュールに何MHzのクロックを入れるかということです。3000psの周期、つまり333MHzのクロックを入れます。

最後にクロックをNoBufferにすればおしまいでs。NoBufferというのは、外部からのクロックピンから直接入れるのではなく内部でMMCMなどを使って作ったクロックで動かすときの設定です。

最初のBlockDesignを見てください。sys_clk_iにはダイアログで設定した333MHzのクロックを入れます。ここに333MHz以上のクロックを入れるとMIGをだましてオーバークロックが試せますが、それはまだ今度の機会にしましょう。

clk_ref_iには200MHzのクロックを入れていますが、これは設定にかかわらず200MHz固定です。XILINXのプリミティブが内部で時間を計るのに使います。

MIGの出力するui_clkは333MHz/8=83.333MHzを出します。8で割るのはDDR3だからです。4:1やデータバス64bit幅というところを変えれば変わるかもしれませんが、どんなバグを踏むかと思うと恐ろしくてできません。データ速度を変えたい場合はAXI Interconnectでやるとよいでしょう。

こうしてデザインを作って、うまくDDR3メモリが認識されて初期化されてキャリブレーションが完了するとinit_calib_completeがHになります。

Spartan-7基板が届いた

2019.12.27

待ちに待ったSpartan-7基板の実装が上がってきました!

令和元年シルクもばっちりです。

さて、電源を入れようと思ったのですが、忘れていました。チップ集合抵抗が実装されていないのです。

手作業で実装し、いざ火入れ!

・・・

・・・

・・・

電源が入らない。

これはやばい!

焦ります。

。

。

安定化電源は5Vで、電流は0.14Aを示しています。だからショートではない。

今回から登場したMOS FETによる電源供給スイッチの回路が悪さしているのでしょうか。

試しにソースとドレインをショートさせてみると、電源が入りました。しばらく回路図を見て原因が分かりました。

P MOS FETを使わなければならないところに、N MOS FETを実装していたのです。

このような問題はありましたが、無事に電源も入りました。

USBチップのCY7C68013Aも認識でき、Spartan-6ボードと同じファームウェアを書き込んでUSB-JTAGを認識させることもできました。

USB-JTAGが認識できたらMITOUJTAGを使ってバウンダリスキャンでFPGAの端子が見えました。

ここまでくれば一安心です。少なくともFPGAは生きていることがわかります。

自分で基板を作る場合、FPGAの端子が見えるとすごく安心できます。

温度も見えました。

自分でFPGA基板を作る場合には「動く」とわかるところまでがストレスの連続なのです。動かなければ基板作り直しで何十万円もドブに捨てることになるわけですから。ZYBOのような既成のボードで使っている限り決して知ることはない苦しみです。

IoTの機器を作る場合も同様。

FPGAの端子が見えれば超安心できますね。

Spartan-7基板が実装完了

2019/12/27

実装が完了し、到着しました。

チップ集合抵抗が実装されていないので、すぐには動かせませんが、今日中には動作確認ができるでしょう。

チップ抵抗のサイズが合わない?

2019/12/24

実装屋さんから電話が来ました。

チップ抵抗のサイズが違うとのことです。基板は3216サイズで、送った物は2125サイズとのこと。

あれ?2125で設計したはずなのに・・。またやってしまった。

Spartan-7基板の生基板が届いた!

2019.12.22

木曜日に出図したSpartan-7基板の生基板が届きました。

12枚面付です。

UPSから荷物が届かないのでチャーターを使った

2019.12.20

Spartan-7ボードの製造で届くはずの部品がUPSから届かないという事態が起きました。

本来は木曜日に届くはずだったのですが、飛行機の乗り継ぎに失敗してアラスカで一日足止めされ、金曜日に成田に来たのですが、通関が12時を超えたため翌日扱いになるという例のパターンです。

すると木曜日に届くはずだった荷物が月曜日に届くという4日遅れになるので、これはどうしても回避しなければなりません。

UPSはおそらく新木場まで来て、新木場で通関処理を行っているのだと思いますが、10時40分に成田だとまず新木場を12時に出るのは間に合いません。

「この動きは怪しい」と思ったらすぐに電話します。

今回、はじめて「チャーター」というのを利用しました。

UPSは12時までに通関しないと午後の運送トラックに乗れないのですが、乗れなかった荷物は翌日のトラックに乗って新木場で待機します。

この荷物を当日受け取るには、新木場へ取りに行くか、バイク便(チャーター)で運んでもらうかです。

チャーターは別途料金が5000円くらいかかりますが、電子部品の価格を考えれば安いものです。

18時半に無事にSpartan-7ボード用の荷物を受け取ることができました。

チャーターを使うには、昼頃に荷物が来ないことを気配で察したらすぐに電話しないといけません。

夕方遅くになって電話をしてもトラックに荷積みしてしまった後では見つけられず間に合わないそうです。

理想的には通関前に電話しておくのがよさそうです。