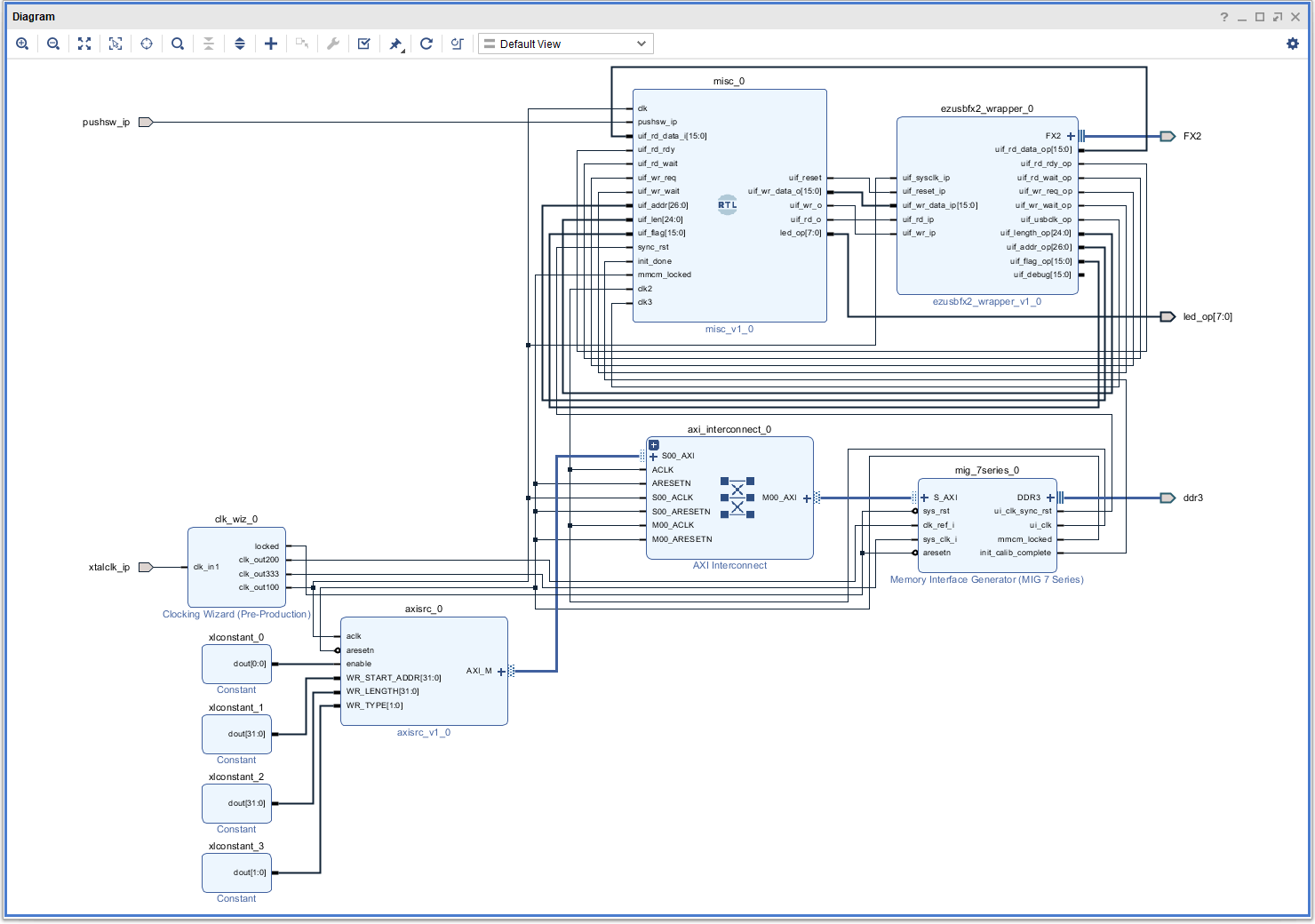

サンプルデザインについて

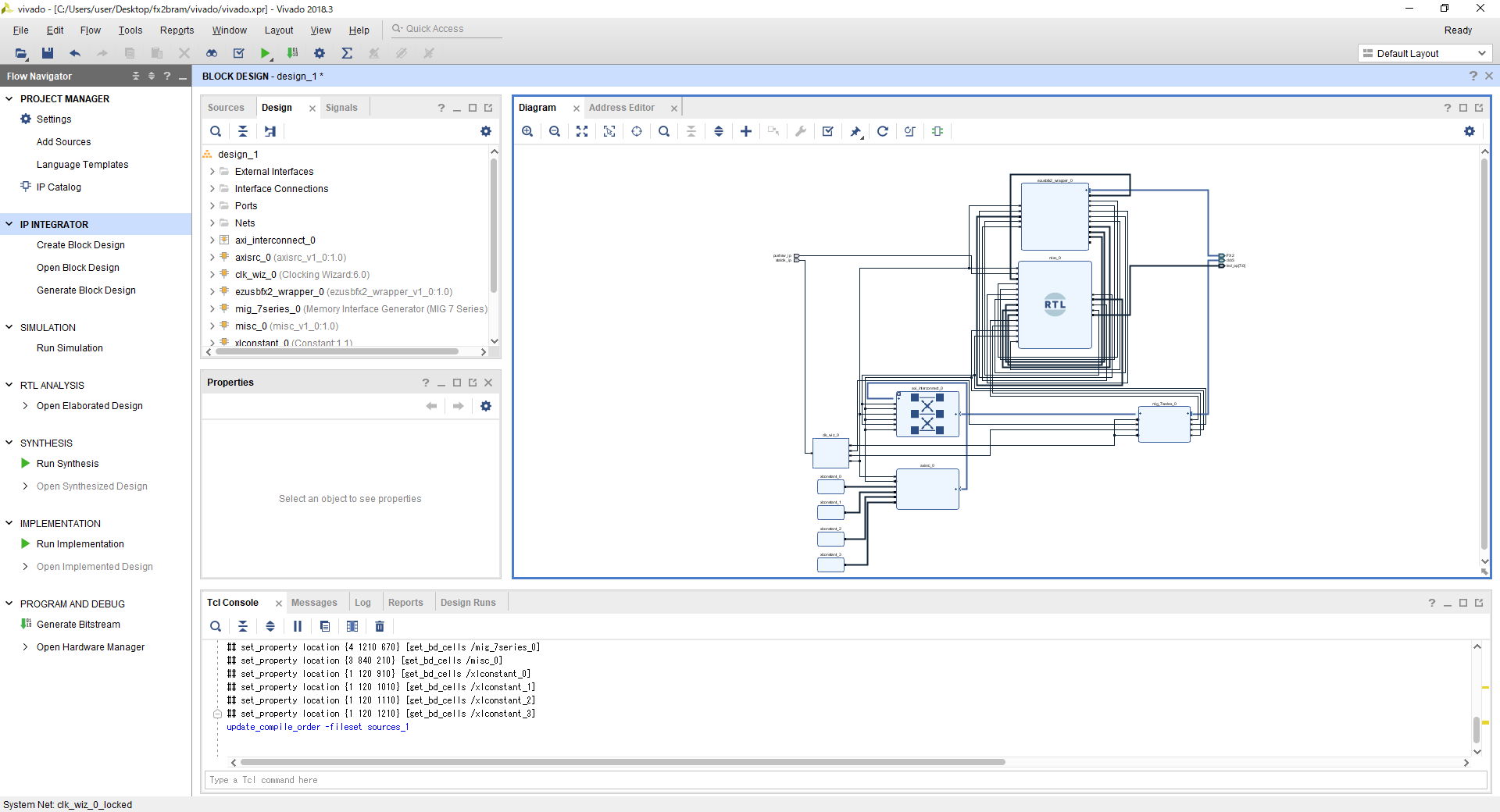

本稿執筆時点(2020年3月2日)におけるサンプルデザインを示します。

このデザインには下記の機能があります。

- USB2.0インタフェースを通じてBlock RAMを読み書きする機能

- USB2.0インタフェースを通じたテストパターン発生回路

- MIGを使用してDDR3メモリにRead/Writeする機能

※なお、現時点では、DDR3メモリは自動的に読み書きしているため、USBからは操作できません。今後は、USBを通じたDDR3メモリの読み書き、GPIOの操作、AXIバスの引き出しなどを予定しています。

ダウンロード

サンプルデザインは下記のURLからダウンロードできます。

http://www.tokudenkairo.co.jp/sp7/fx2bram.zip

プロジェクトのビルド方法

プロジェクトのアーカイブについて

このプロジェクトはNahiVivaというツールを使ってアーカイブされているため、約300kバイトという驚異的に小さなサイズで配布することができています。

圧縮ファイル内にはVivadoのXPRプロジェクトやBlockDesignは入っておらず、XPRやBDを生成するためのTCLスクリプトが入っています。TCLスクリプトはユーザがマウスやキーボードでプロジェクトの生成する際の操作を記録したものなので、小さいサイズで配布することが可能となります。

Vivadoのバージョンとフォルダの設定

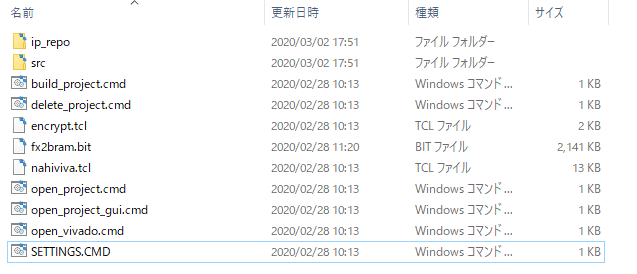

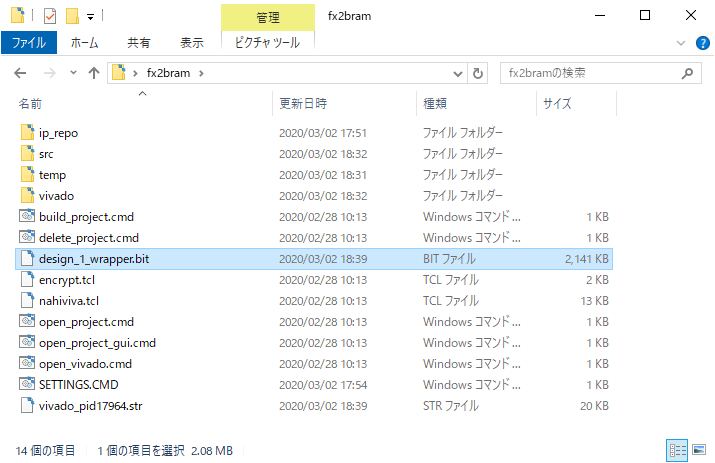

圧縮ファイルを解凍すると下の図のようなファイルが現れます。

まずこの中のSETTINGS.CMDを編集します。デフォルトでは下のようになっているので、Vivadoをインストールしたフォルダとバージョンを書き換えます。

@SET VIVADO_PATH=D:\Xilinx\Vivado\ @SET VIVADO_VERSION=2019.2

例えば、D:\Xilinx\VivadoにインストールしたVivado 2018.3を使用する場合は以下のようにします。

@SET VIVADO_PATH=D:\Xilinx\Vivado\ @SET VIVADO_VERSION=2018.3

次に、src\design_1_bd.tclというBlockDesignの元になるファイルがあるので、この23行目にあるバージョン番号を書き換えます。

################################################################

# Check if script is running in correct Vivado version.

################################################################

set scripts_vivado_version 2019.2

set current_vivado_version [version -short]

Vivado2018.3へのダウングレード

当プロジェクトはVivado 2019.2用に構築されていますが、以下の個所を修正することでVivado 2018.3で開くことができるようになります。

① src/create_project.tclの120行目

set_property -name "platform.description" -value "Vivado generated DSA" -objects $obj

をコメントアウトします。

② src/design_1_bd.tclの375行目

set xtalclk_ip [ create_bd_port -dir I -type clk -freq_hz 50000000 xtalclk_ip ]

を、2行に分けます。

set xtalclk_ip [ create_bd_port -dir I -type clk xtalclk_ip ] set_property CONFIG.FREQ_HZ 50000000 [get_bd_ports xtalclk_ip]

とします。

③ src/design_1_bd.tclの375行目

assign_bd_address -offset 0x80000000 -range 0x20000000 -target_address_space [get_bd_addr_spaces axisrc_0/AXI_M] [get_bd_addr_segs mig_7series_0/memmap/memaddr] -force

から-forceを削除し、

assign_bd_address -offset 0x80000000 -range 0x20000000 -target_address_space [get_bd_addr_spaces axisrc_0/AXI_M] [get_bd_addr_segs mig_7series_0/memmap/memaddr]

とします。

④ src/create_project.tclの251行目付近と277行目付近にある2019という文字を2018にします。(計4か所)

create_run -name synth_1 -part xc7s50csga324-1 -flow {Vivado Synthesis 2018} -strategy "Vivado Synthesis Defaults" -report_strategy {No Reports} -constrset constrs_1

} else {

set_property strategy "Vivado Synthesis Defaults" [get_runs synth_1]

set_property flow "Vivado Synthesis 2019" [get_runs synth_1]

create_run -name impl_1 -part xc7s50csga324-1 -flow {Vivado Implementation 2019} -strategy "Vivado Implementation Defaults" -report_strategy {No Reports} -constrset constrs_1 -parent_run synth_1

} else {

set_property strategy "Vivado Implementation Defaults" [get_runs impl_1]

set_property flow "Vivado Implementation 2019" [get_runs impl_1]

プロジェクトの生成

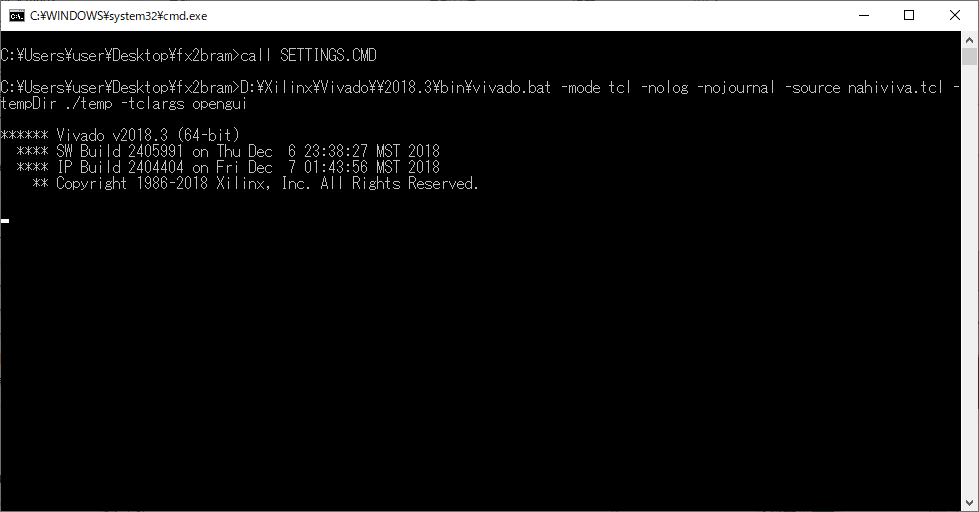

VivadoのプロジェクトであるXPRを生成するため、open_project_gui.cmdを実行します。

下の図のようなDOSプロンプトが表示され、裏でVivadoが起動します。

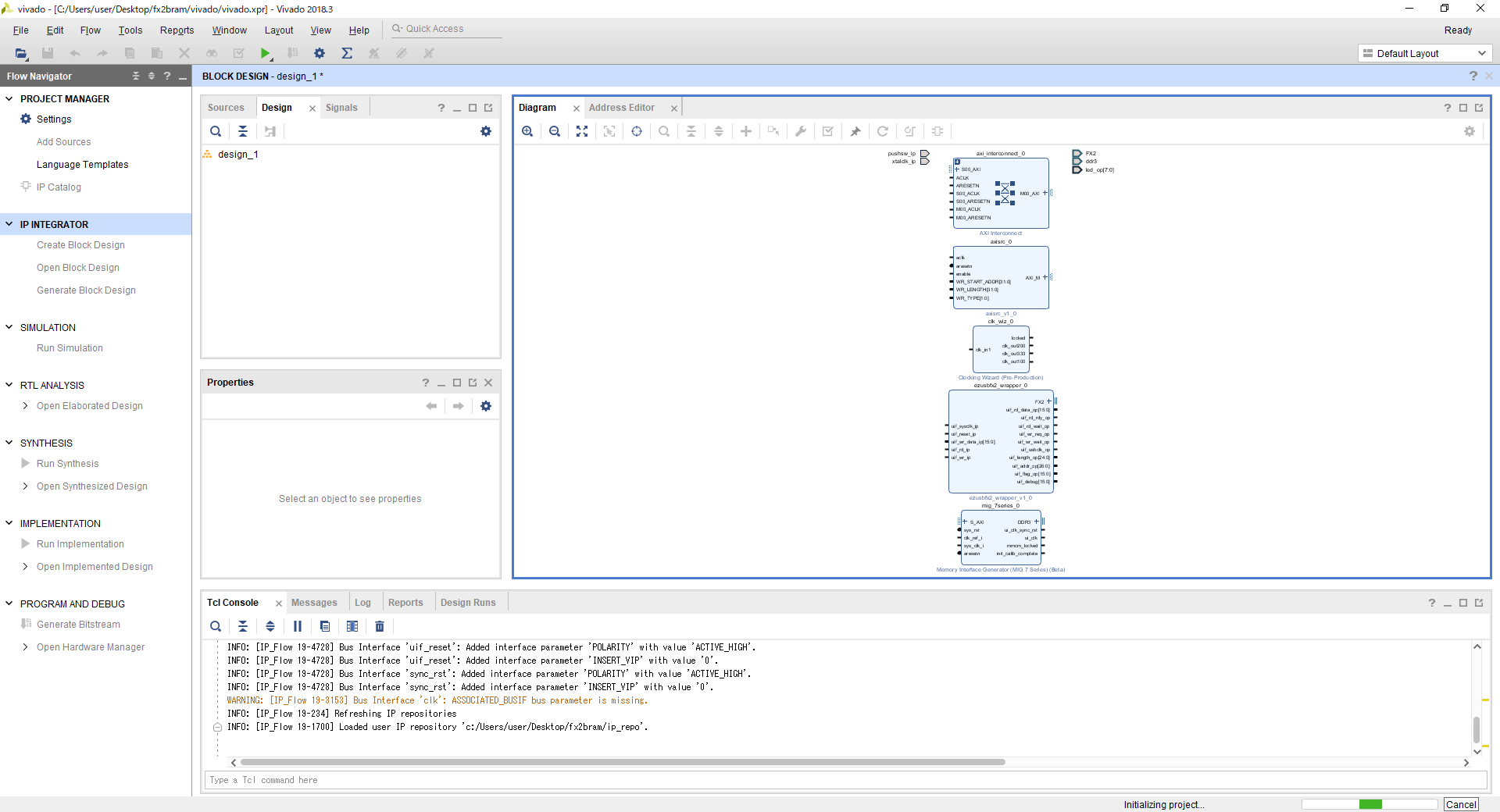

様々なコンポーネントが置かれ、パラメータが設定され、配線が自動的に接続されていきます。

プロジェクトの生成に失敗した場合は・・

Vivadoフォルダを削除してください。

NahiVivaを使う場合はVivadoフォルダ配下には重要なファイルは配置されません。そのため、巨大化し不安定にもなるVivadoフォルダを削除しても問題はありません。

Vivadoフォルダを削除することに不安があればdelete_project.cmdを実行し、yを押してください。

プロジェクトの論理合成

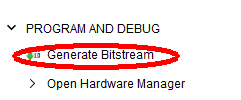

Generate BitStreamを行うことで論理合成が行われます。

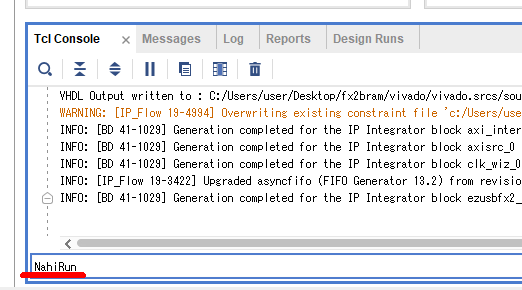

TCLコンソールからNahiRunと入力としても論理合成が行われます。NahiRunではUpdate IPの処理を同時に行うことができるので、極力NahiRunを使ってください。

Generate Bitstreamを行う場合

NahiRunを行う場合

TCLコンソールにNahiRun -updateと入力します。

最初の一回目のビルドではIPの生成を行うため長い時間がかかりますが、2回目からは比較的早くビルドが行われます。

生成されたファイルの場所

Generate Bitstreamで生成されたBitStreamファイルは\fx2bram\vivado\vivado.runs\impl_1にdesign_1_wrapper.bitとしてあります。

NahiRunで生成した場合は、プロジェクトのトップフォルダ(fx2bram\)にdesign_1_wrapper.bitがコピーされます。