サンプルデザイン

サンプルデザインについて

本ボードに用意されたサンプル・リファレンス・デザインは、USB経由でFPGAの内部ロジックと通信を行い、動作テストを行います。主な機能は下記のとおりです。

- USBの動作テスト

テストパターンや、DDR2 SDRAMの内容、BlockRAMの内容、GPIOの値を読み出せます。

読みだしたデータは、VGAサイズの画像として表示させることができます。

- DDR2 SDRAMの動作

USB経由で最大64Mバイトのデータを読み書きできます。

- I/Oピンヘッダのオープン・ショート・テスト

64個のI/Oピンヘッダのうち、どれか1個がLレベルに、その他はHレベルにします。

USBで読みだす際には、ハイインピーダンスになります。

この機能は、オシロスコープなどをピンに当てておくことでピンヘッダがショートや断線していないかどうかを調べるための検査に使います。

- LEDの表示

D7は、DDR2 SDRAMから読み出し中であることを表します。

D8は、DDR2 SDRAMに書き込み中であることを表します。

SW1を押すと、D1〜D6がバイナリ・カウント・アップします。

サンプルデザインは、専用のsp6test.exeを使用して操作します。

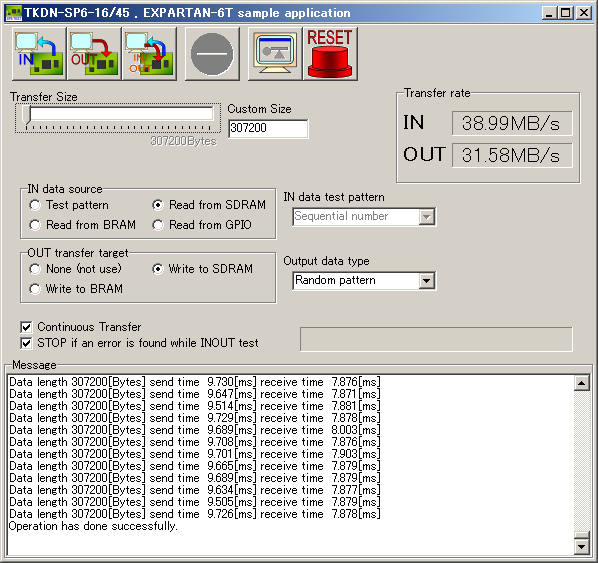

sp6test.exeの動作中のイメージを下記の図に示します。

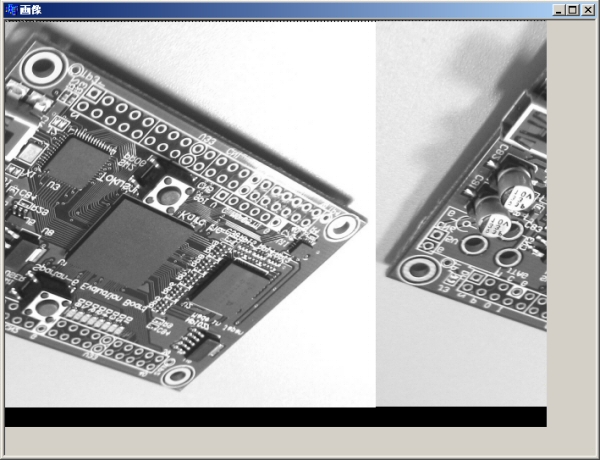

DDR2 SDRAMにあらかじめ画像データなどを転送しておくと、下の図のように画像として表示することができます。

サンプルデザインの更新履歴

Version2.6 (平成23年12月15日)

■FPGAに関すること

(1) DDR2メモリアクセスの部分をMCBに対応させました。安定性が格段に向上しました。

Version2.3+ (平成23年4月7日)

■FPGAに関すること

(1) Verilog版のサンプルデザインを追加しました

Version2.3 (平成23年2月14日)

■DLLに関すること

(1) Windows7 x64用ドライバに対応

(2) Windows7で表示したときに画面が崩れる問題を修正

Version2.2 (平成22年10月4日)

■FPGAに関すること

(1) 低温時に、USBの通信データにエラーが出る現象を改善

(2) 16MBytesを超えるUSBの通信も正常に動作するようにした

(3) SDRAMコントローラをマルチポート化した

(4) USBからSDRAMの任意のアドレスを読み書きできるようにした

(5) SDRAMコントローラのソースコードを含めた

■DLLに関すること

(1) Read/Writeが5秒でタイムアウトするようにした

(2) USBReset()関数を追加し、フリーズした転送を中断できるようにした。

(3) 16MBytes以上の転送も実行できるようにした

(4) 起動時にSmartJTAGモードではなく、ユーザ通信モードになるようにした

(5) 2つ以上のスレッドが同時にRead/Writeしないよう排他ロックをかけた

(6) DLL内での動的なメモリの割り当てを最適化し、IN/OUT転送を高速化した

(7) 小さなOUT転送で無駄なデータを転送せず、必要最少量のサイズで転送するようにした

■サンプルアプリに関すること

(1) 16MBytesを超えるデータの読み書きも正常にできるようにした

(2) テストパターンの種類を増やした

(3) 最大128MBytesまでのIN/OUTテストが行えるようにした

(4) SDRAMの読み書きアドレスを変更できるようにした

(5) INOUTテストでエラーが出た場合に、INのリトライを行うようにした

(6) マルチスレッド化した

(7) リセットボタンを追加した

設計を更新するための手順

- リファレンスデザインの中にある新しいUSBコア(ezusbfx2_ctrl.ngc)を、お客様が作成したデザインの中にある古いezusbfx2_ctrl.ngcに上書きして置き換えてください。

- USBコアをインスタンシエートするHDLソースの中にuif_addr_op[24:0]の記述があれば、それを[26:0]に書き換えてください。

- FPGAのデザインを論理合成しなおしてください。

- リファレンスデザインの中にある新しいDLL(tkusb.dll)を、お客様が作成したソフトウェアのディレクトリにコピーし、上書きしてください。

サンプルデザインのトラブルシュート

-3グレードのFPGAでUSBの通信エラーが頻発する

Version2.1のUSBコアを使ったデザインでFPGAの速度グレードを上げたところ、USBの通信エラーが発生するようになりました。この問題はVersion2.2で解決しましたので、アップデートしてください。

温度が低いときにUSBの通信エラーが発生する

半導体は温度が下がると高速になるため、前述のエラーが発生するものと思われます。

この問題はVersion2.2で解決しましたので、アップデートしてください。

DDR2メモリへのクロックが出力されない

ISE12.1でのみ起きる現象です。ISE12.2へアップデートするか、ISE11.xを利用してください。

いくつかのタイミングが満たされない

実害はございませんが、タイミングエラーが出ます。この問題を解決するべく、只今改良を行っています。

DDR2メモリの読み書きテストをすると、エラーが出る。

当社製のDDR2コアでは、DDR2メモリの読み出しタイミングが正しい場所に合っていないため、温度変化や個体差によってはエラーが出ます。この問題を解決するべく、只今改良を行っています。

TKDN−SP6-16/45ではMCBが使用できるので、MCBを使用するデザインに改良するのも良いかと思われます。

動作中に熱くなる

本ボードはパソコンのUSBポートとボード上回路を保護するため、USBからの給電ラインに定格500mAのリセッタブル・ヒューズを採用しています。もし、動作電流が500mAを超える状態が継続して続くと、オンボードの保護素子が働いて電源電圧が低下し動作が停止してしまいます。

サンプルデザインはDDR2 SDRAMを使用するため消費電流が多くなります。サンプルデザインを動作させた場合の電流は500mAは越えませんが、できるだけACアダプタから給電するようにしてください。